## スパッタエピタキシー法による SiGeHEMT の低温成膜プロセスの評価

Evaluation of low-temperature deposition process of SiGeHEMT by Sputter Epitaxy Method 東京農工大院工  $^1$ ,情報通信研究機構  $^2$ , $^\circ$ 大久保克己  $^1$ ,本橋叡  $^1$ ,

出蔵恭平1, 広瀬信光2, 笠松章史2, 松井敏明2, 塚本貴広1, 須田良幸1

Tokyo Univ. of Agric. & Technol.<sup>1</sup>, National Inst. of Information and Communications Technol.<sup>2</sup>, °K. Okubo<sup>1</sup>, A. Motohashi<sup>1</sup>, K. Degura<sup>1</sup>, N. Hirose<sup>2</sup>, A. Kasamatsu<sup>2</sup>, T. Matsui<sup>2</sup>, T. Tsukamoto<sup>1</sup>, and Y. Suda<sup>1</sup>

E-mail: sudayos@cc.tuat.ac.jp

【はじめに】我々はこれまでに、歪 Si チャネルを用いたショットキーゲート型 SiGe HEMT(High Electron Mobility Transistor)の作製を目標とし、環境軽負荷型のスパッタエピタキシー法 $^{[1]}$ を用いた歪緩和 4 層 SiGe バッファを提案し $^{[2]}$ 、化学気相成長法などと比較して良好な結晶特性を実現している $^{[3]}$ 、今回は、バッファ層の良好な緩和特性と、電子供給層の低温成膜によるドーパントの拡散抑制を両立可能な成膜プロセスを考案し、作製した HEMT 構造の電子移動度及びキャリア面密度を評価したので報告する.

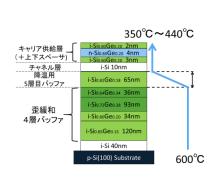

【実験方法】 歪緩和 4 層 SiGe バッファの最適成膜温度として  $600^{\circ}$ Cを提案した [4]. それに対し,電子供給層はドーパントの熱拡散を抑制し急峻なドーププロファイルを形成するために,より低温下での成膜が求められる。しかし,成膜を中断して降温するプロセスでは界面に酸素が混入してしまい,デバイスの性能に悪影響を与えることが予想される。そこで今回は,歪緩和 4 層 SiGe バッファと歪 i-Si チャネルの間に 5 層目の SiGe 層を成膜し,その間に成膜温度を下げるプロセスである図 1 の構造を考案し,電子供給層の成膜温度を 350,380,410,440 $^{\circ}$ Cで作製した。各試料は歪 i-Si チャネルの歪率を X 線回折法,平坦性を原子間力顕微鏡(AFM),移動度とキャリア面密度をホール効果測定によって評価し,本研究で用いている HEMT 構造の電子供給層の最適成膜温度を検討した。

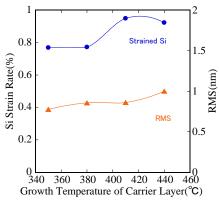

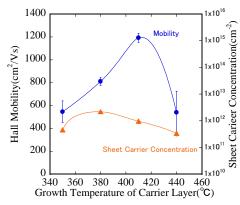

【結果と考察】図 2 に、電子供給層の成膜温度に対する歪 i-Si チャネルの歪率と試料最上部の表面ラフネス(RMS 値)を示す。これよりいずれの成膜温度でも歪 i-Si は移動度向上効果が飽和する 0.7 以上の歪率  $^{[5]}$ の取得が確認された。また、成膜温度が高くなるほど試料最上部の表面ラフネス(RMS 値)が高くなることが判明した。これは、バッファの緩和が進行しているため、成膜温度が高いほど試料に与えられるエネルギーが大きくなり、転位が発生して表面ラフネスが悪化したと予測される。次に、電子供給層の成膜温度に対する電子移動度とキャリア面密度を図 3 に示す。これより、移動度は 410℃付近、キャリア面密度は 380℃付近で最大となることが判明した。移動度については結晶性とドーパントの拡散、キャリア面密度は活性化率とドーパントの拡散の影響が原因として予測される。電子供給層の成膜温度 410℃の試料で、最大移動度 1230cm²/Vs、キャリア面密度  $9.7\times10^{11}$ /cm² と本スパッタエピタキシー法で作製した HEMT 構造で、CVD 法で作製された他の HEMT 構造と比較しても遜色のない特性が得られた。

【謝辞】この研究の一部は,情報通信研究機構先端 ICT デバイスラボで実施された.

図 1 SiGeHEMT 構造

図2 電子供給層の成膜温度に対する 歪 i-Si チャネルの歪率と 試料最上部の表面ラフネス

図3 電子供給層の成膜温度に対する 電子移動度とキャリア面密度

[1] H. Hanafusa *et al.*, *Jpn. J. Appl. Phys.*, **47** (2008) 3020. [2] H. Maekawa *et al.*, *J. Cryst. Growth*, **301/302** (2007) 1017. [3] H. Hanafusa *et al.*, *Appl. Phys. Express*, **4** (2011) 025701. [4] 出藏ら, 15p-P11-10, 第 77 回応用物理学会学術講演会 (新潟, 2016) [5] T. Manku *et al.*, IEEE Trans. Electron Devices, Vol. 39, No.9, pp2082-2089, Sep. 1992