## 真空蒸着法により作製した a-Si/BaSi2の接触抵抗低減効果

Reduction of Contact Resistance of a-Si/BaSi<sub>2</sub> Deposited by Vacuum Evaporation 須原 貴道¹、○中川 慶彦¹、原 康祐²、黒川 康良¹、末益 崇³、宇佐美 徳隆¹ (1. 名古屋大、2. 山梨大、3. 筑波大)

T. Suhara<sup>1</sup>, °Y. Nakagawa<sup>1</sup>, K. O. Hara<sup>2</sup>, Y. Kurokawa<sup>1</sup>, T. Suemasu<sup>3</sup>, N. Usami<sup>1</sup>

(1. Nagoya Univ., 2. Univ. of Yamanashi, 3. Univ. of Tsukuba)

E-mail: nakagawa.yoshihiko@f.mbox.nagoya-u.ac.jp

【緒言】資源制約の少ない BaSi2 は、単接合薄膜太陽電池に適した光吸収係数とバンドギャップ値 を有していることから注目されている[1]。 近年、分子線エピタキシー(MBE)法で作製した BaSi₂膜 の表面を a-Si 層のキャッピングにより自然酸化膜の生成を抑制され、接触抵抗値の低減および太 陽電池変換効率の向上が報告された[2]。MBE 法よりも低い真空度で製膜可能な真空蒸着法におい ても、蒸着後の残留原料の再加熱によって *In-situ* で a-Si 層が堆積され、キャリアライフタイムが 向上することが報告された[3]。本研究では、真空蒸着法において、試料ボートを二つ用いること による極薄 a-Si 層の堆積と、接触抵抗軽減効果について報告する。

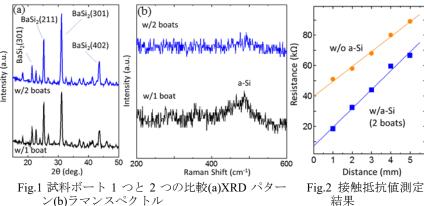

【実験方法】二つの W 製試料ボート A、B を用い、BaSi<sub>2</sub> ソースを A には 0.015 g、B には 0.135 g をのせた。まず、基板温度 600 ℃ で A、B の順番に 140 A を通電して BaSi₂ を堆積し、その後基 板温度 400 ℃ で A に 150 A を通電し、a-Si 層を堆積した。比較のため、0.15 g のソースをのせた 試料ボート1つのみを用いて a-Si 層を堆積した試料も作製した。X線回折、ラマン分光分析を用 いた構造分析と、TLM(Transfer Length Method)法を用いて接触抵抗測定を行った。

【結果と考察】X線回折パターンを Fig.1(a)に示す。どちらの試料も BaSi2のピークが確認された。 ラマンスペクトルを Fig.1(b)に示す。試料ボートを一つのみ用いた試料では、a-Si 由来のブロード ピークが確認でき、二つ用いた試料も若干ではあるが a-Si のブロードピークが確認できる。これ らのことから、試料ボートを二つ用いることで Si 基板上の BaSi2薄膜上に薄い a-Si 層を堆積でき たことが分かる。接触抵抗値測定の結果を Fig.2 に示す。a-Si 層でキャッピングをしていない試料 に比べ、薄い a-Si 層でキャッピングをした試料は接触抵抗値が低減している。これらのことから、 真空蒸着法による、試料ボートを二つ用いた In-situ での a-Si 層キャッピングは有効であることが

判明した。

8

[1] K. Toh, et al., Jpn. J. Appl. Phys. **50**, 068001 (2011). [2] S. Yachi, et. al., Appl. Phys. Lett. 109, 072103 (2016). [3] 原他、第77回応用物理学 会秋季学術講演会 15a-B3-