# 傾斜型フィールドプレートによる InGaAs 系 HEMT 中の電子速度への影響

### Influence of slant field plates on electron velocity in InGaAs-HEMTs

## 東北大通研, ○細谷 友崇、尾辻 泰一、末光 哲也

RIEC, Tohoku Univ., °T. Hosotani, T. Otsuji, T. Suemitsu

E-mail: tomo@riec.tohoku.ac.jp

#### 1, はじめに

InGaAs 系 HEMT はミリ波・サブミリ波帯でのキーデバイスとして注目されている。しかし、InGaAs の狭いバンドギャップからデバイスの耐圧は低下する。これは、HEMT を用いて電力増幅器を構成した際の動作電圧を制限し、増幅器の出力や効率を高める上で不利である。我々はゲート電極に傾斜型フィールドプレート(FP)を導入し、デバイスのドレイン-ソース耐圧を高める手法を報告した [1]。しかし、耐圧は高くなったものの、電流利得遮断周波数( $f_T$ )は低下した。本発表では、FP を有する InGaAs 系 HEMT について遅延時間解析を行い、真性遅延時間から電子速度を抽出し、FP が電子走行に与える影響について報告する。

#### 2, デバイス構造・測定結果・考察

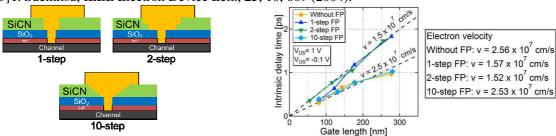

デバイス試作にはMOCVDにより成長した InAlAs/InGaAs HEMTエピタキシャル基板を用いた。 ゲート電極には SiCN を用いて形成した FP を導入した [1]。SiCN 堆積時のキャリアガス流量を変化させることで、Fig. 1 に示すような 1-step、2-step、10-step の 3 種の FP を試作した。また、デバイスの高周波特性向上を目指して、InP エッチストップ層を Ar プラズマエッチングにより除去する二段階リセス構造 [2]も導入した。実ゲート長は集束イオンビーム(FIB)により測定した。

真性遅延時間を[3]に示された手法により測定した。Fig. 2 に各 FP 構造によるゲート長( $L_g$ )と真性遅延時間( $\tau_{int}$ )の結果を示す。外挿すれば原点を通る直線となり、実効電子速度を  $v_{eff}$  とした時の真性遅延時間の定義  $\tau_{int}$ = $L_g$ / $v_{eff}$  からも妥当といえる。FP 無しのものと比較し 10-step 型はほぼ同じ傾向であったのに対し、1-step 型と 2-step 型は真性遅延が大きく増加した。外挿の傾きの逆数から求めた電子速度  $v_{eff}$  を Fig. 2 右側に示す。FP 無しと 10-step 型はともに理論値(2.5 x  $10^7$  cm/s)とほぼ等しい値となっているのに対し、1-step 型と 2-step 型は理論値から約 40%低い値となっていた。

FP 導入による  $f_T$ 低下原因の1つとして1-step型と2-step型は電子速度低下が考えられる。一方、10-step型に関しては電子速度には影響せず、寄生遅延など電子速度以外による  $f_T$ 低下を考えることができる。また、10-step型は電子加速特性に影響を与えることなくドレイン - ソース間電界集中を緩和しているといえる。

### 3, まとめ

従来の FP 構造に近い 1-step 型と 2-step 型では電子速度が低下し、HEMT の高周波特性を大幅に低下させる要因になることが分かった。それに対して、傾斜型 FP である 10-step 型では電子速度の低下が見られず、ミリ波帯等の高周波用 FET に導入する FP として最適であると言える。

- ○謝辞 本研究は、総務省 SCOPE (No.165003013) の支援により行われた。本研究で用いたデバイスの作製は、東北大通研附属ナノ・スピン実験施設で行われた。

- [1]T. Hosotani, T. Otsuji, and T. Suemitsu, Appl. Phys. Express, 9, 114101 (2016).

- [2]T. Suemitsu, et al, IEEE Trans. Electron Devices, 49, 10, 1694 (2002).

- [3]T. Suemitsu, IEEE Electron Device Lett., 25, 10, 669 (2004).

Fig. 1. 試作した3種のFP構造

Fig. 2. 各FP構造の実ゲート長による真性遅延時間と電子速度