## Al<sub>2</sub>O<sub>3</sub>超薄膜膜介在層を有する SiO<sub>2</sub>/InAIN 界面の特性(2)

Properties of SiO<sub>2</sub>/InAlN interface having ultrathin Al<sub>2</sub>O<sub>3</sub> interlayer (2)

北大量子集積エレ研<sup>1</sup> O(M2) 北嶋翔平<sup>1</sup>,赤澤正道<sup>1</sup>

RCIQE, Hokkaido Univ.<sup>1</sup>, °Shouhei Kitajima<sup>1</sup>, Masamichi Akazawa<sup>1</sup>

E-mail: kitajima@rciqe.hokudai.ac.jp

【はじめに】GaN に格子整合する InAIN は、GaN 系 HEMT のバリア材料として有望であるが、リーク電流が課題である。絶縁ゲート HEMT とすることでリーク電流の低減[1]、さらには高い遮断周波数が達成されている[2]。しかし、絶縁体一半導体界面の物性については未解明の部分が多い。本報告においては、 $SiO_2$  と InAIN の界面を、 $Al_2O_3$  超薄膜層により制御した構造に対して、界面における物性の評価を行った結果を報告する。

【実験方法】サファイア基板上に GaN バッファ層を介して MOVPE 成長された InAIN を用いた。オーミックコンタクト形成後、 $300^{\circ}$ Cにおいて  $0.5~\rm nm$  あるいは  $1~\rm nm$  の  $Al_2O_3$  を ALD により堆積し、その後プラズマ CVD を用いて  $SiO_2$  を厚く( $\sim 20~\rm nm$ ) 堆積し、電極を蒸着して MOS 構造とした。プロセスの各段階で XPS による試料表面の評価を行い、完成後の MOS ダイオードに対して C-V 測定による評価を行った。

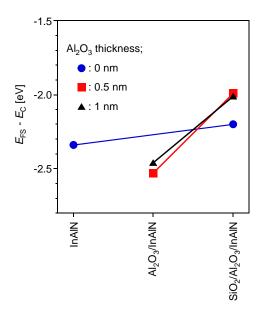

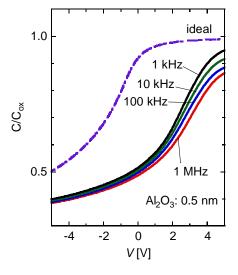

【結果】Fig.~1 は、XPS により試料の表面フェルミ準位の位置を、各プロセス段階において評価した結果である。 $Al_2O_3$  超薄膜堆積により、表面フェルミ準位位置が深くなり、その後の  $SiO_2$  堆積により浅い方向にシフトする現象が観測された。これには、 $Al_2O_3$  超薄膜内あるいは最表面に存在する電荷が関与している可能性が高い。Fig.~2 には、 $Al_2O_3$  を 0.5 nm 挿入した MOS ダイオード完成後の C-V 特性を示す。1 MHz の曲線からは低い界面準位密度が導出されるが、特有の周波数分散が見られる。その原因については検討中である。

【謝辞】本研究は、科学研究費助成事業基盤研究(C)(15K04672)の援助を受けた。

- [1] G. Pozzovivo et al., Appl. Phys. Lett. 91, 043509 (2007).

- [2] Y. Yue et al., IWN2012, SLN-3 (2012).

**Fig. 1** Surface Fermi level position measured by XPS at each process step.

**Fig. 2** *C*–*V* characteristics obtained for metal/SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/InAlN diode.