## 伸張歪み Si/緩和 SiGe/Si(110)へテロ構造の

## ゲート電圧印加 Hall 測定による移動度評価

Mobility evaluation of tensile-strained Si/relaxed SiGe/Si(110) heterostructures using gate-voltage-applied Hall measurement

山梨大1, 東京都市大総研2

○(M1) 浪内大地 ¹, 佐藤圭 ¹, 澤野憲太郎 ², 有元圭介 ¹, 山中淳二 ¹, 原康祐 ¹, 中川清和 ¹ Yamanashi Univ.¹, ARL Tokyo City Univ.²

°D. Namiuchi<sup>1</sup>, K. Sato<sup>1</sup>, K. Sawano<sup>2</sup>, K. Arimoto<sup>1</sup>, J. Yamanaka<sup>1</sup>, K. O. Hara<sup>1</sup>, K. Nakagawa <sup>1</sup> E-mail: g18tz013@yamanashi.ac.jp

CMOS デバイスの高性能化、低消費電力化を実現するために、正孔移動度を向上させる 必要がある。(110)面を表面に有する伸張歪み Si は正孔有効質量を無歪み Si の半分以下にできるという計算結果がある。実際に我々の作製した伸張歪み Si チャネル p-MOSFET の電気 特性評価より、高い実効移動度が得られる事を確認した。本研究では、ゲート電極付き Hall Bar (以下 G-Hall と称する)を用いてゲート電圧印加下において Hall 測定を行い、正孔移動度の評価を試みた。Hall 測定では CV 測定を用いず、四端針法による測定であるため、寄生容量やコンタクト抵抗の影響を受けずに評価できる利点があると考えられる。

測定した試料の結晶成長は、固体ソース MBE を使用し n-Si(110)基板上に階段傾斜組成 SiGe 層(Ge 組成:  $3\sim30\%$ )および均一組成 SiGe 層(Ge 組成: 30%)を各 200 nm を堆積後、Si 層を 20 nm 堆積させた。その後、フォトリソグラフィ法により p-MOSFET と G-Hall を同時に作製した。

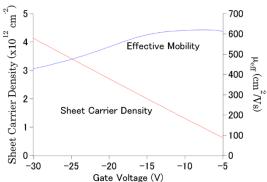

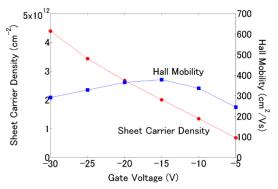

Fig.1 と Fig.2 に同一試料上に作製された p-MOSFET の電気特性評価と G-Hall のゲート電圧印加 Hall 測定の解析結果をそれぞれ示す。シートキャリア密度は p-MOSFET の結果と同様である事を確認できた。またゲート電圧が-15V 以下の範囲において移動度が低下するという傾向が一致した。しかし実効移動度と Hall 移動度の値には大きな差が生じた。この原因については調査中である。

Fig. 1 Carrier density and hole mobility obtained by IV and split CV measurements on pMOSFET.

Fig. 2 Carrier density and hole mobility obtained by gate-voltage-applied Hall measurement.