# Effects of Wet O<sub>2</sub> Annealing on the Transfer Characteristics of Solution Processed

### Amorphous Indium Zinc Oxide Thin-film Transistors

## NAIST<sup>1</sup>, <sup>O</sup>(D2)Michael Paul A. Jallorina<sup>1</sup>,

## Juan Paolo S. Bermundo<sup>1</sup>, Mami N. Fujii<sup>1</sup>, Yasuaki Ishikawa<sup>1</sup>, and Yukiharu Uraoka<sup>1</sup>

#### E-mail: michael.jallorina.mf8@ms.naist.jp

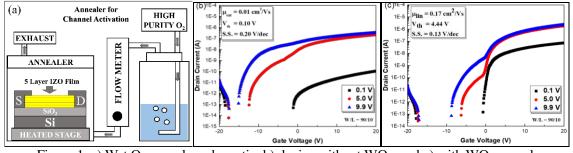

Research on transparent amorphous oxide semiconductor (TAOS) materials have seen a dramatic rise in activity ever since its introduction<sup>1</sup>. Different materials such as IGZO, HIZO, and IZO have been explored by acting as the switching element in active matrix displays<sup>2</sup>. The devices produced need to be annealed at temperature  $\geq 300^{\circ}$ C to remove any existing defects during the fabrication process<sup>1</sup>. There has also been growing interest in lowering the device fabrication process temperature to enable deposition on low thermal budget, flexible, and transparent substrates. In a previous study, we have demonstrated that low temperature annealing (150°C) of IGZO devices in a humid environment (wet O<sub>2</sub> annealing – WO<sub>2</sub>) can significantly enhance the TFT's electrical characteristics by improving the M-O network and decreasing oxygen vacancies<sup>3</sup>. In this work, solution processed IZO TFTs were fabricated at a maximum process temperature of 250°C Furthermore, the electrical characteristics of devices subjected to channel layer activation using a humid annealing environment were investigated and compared to those that were not.

IZO films were fabricated by spin coating a 77:23=In:Zn solution on a Si substrate with 100 nm SiO<sub>2</sub> which serves as the bottom gate and dielectric respectively. Formed films have a nominal thickness of 40-50nm. Patterning was performed via photolithography and wet etching. Two sets of devices were fabricated at a max process temperature of 250°C. The fabricated devices were split into two groups: w/o WO<sub>2</sub> anneal and w/ WO<sub>2</sub> anneal after the channel formation step. Then, the Mo(80nm)/Pt(20nm) source/drain electrodes were deposited via sputtering and were patterned via the lift-off technique. Afterwards, the devices were annealed in an O<sub>2</sub> environment for 1 hour and were also cooled down in the same environment. Finally, electrical characteristics were measured by using an Agilent 4156C semiconductor parameter analyzer.

Both devices exhibit switching behavior but the WO<sub>2</sub> annealed devices exhibited less negative shifting of the threshold voltage ( $V_{th}$ ) and higher  $I_{ou/off}$  ratios compared to the devices which did not undergo channel activation. During the channel activation step, the humid annealing environment may help in decreasing oxygen deficiencies, point defects, and help in the formation of higher percentage M-O networks, as evidenced in our previous study<sup>3</sup>. This may be explained by the suppression of the outward diffusion of oxygen related molecules as well as increased diffusivity of water vapor during the channel activation process. Despite the improvement in the electrical characteristics, noticeable humps can be observed especially at higher drain voltages which may be a manifestation of donor-like traps due to the annealing condition. Thus further tests such as secondary ion mass spectroscopy (SIMS), positive bias stress (PBS) and negative bias stress (NBS) tests should be done to identify the cause.

Figure 1. a) Wet  $O_2$  annealer schematic, b) device without  $WO_2$ , and c) with  $WO_2$  anneal. Characteristics are measured for  $V_d = 0.1V$ .

Acknowledgements: We wish to thank our research collaborators from Nissan Chemical Corporation for providing the IZO solution and other materials used in this research.

[1] T. Kamiya, K. Nomura, and H. Hosono, Science and Technology of Advanced Materials 11, 044305 (2010).

[2] J.S. Park, W.-J. Maeng, H.-S. Kim, and J.-S. Park, Thin Solid Films 520, 1679 (2012).

[3] M.P.A. Jallorina, J.P.S. Bermundo, M.N. Fujii, Y. Ishikawa, and Y. Uraoka, Applied Physics Letters 112, 193501 (2018).