## 中空構造 SOI 層を用いた低温転写によるフレキシブル基板上での 単結晶シリコン CMOS 回路作製プロセスの構築

Single Crystalline Silicon CMOS Circuit Fabrication on Flexible Substrate by Meniscus Force Mediated Layer Transfer Technique

## 広大院端研 °水上 隆達, 山下 知徳, 東 清一郎

Graduate School of Advanced Sciences of Matter, Hiroshima Univ.

°R. Mizukami, T. Yamashita and S. Higashi

E-mail: semicon@hiroshima-u.ac.jp

**序>**ウェアラブルデバイス等に代表されるフレキシブルエレクトロニクスは近年より一層注目を集めており、有機物や酸化物半導体など様々な材料を用いて研究開発が行われている。[1] このように一枚の基板上における異種材料のハイブリッドはフレキシブルエレクトロニクスの発展において極めて重要である。上述のように様々な材料が採用されているが、CMOS 回路の形成において高い移動度、高い信頼性、そして CMOS 集積可能な単結晶シリコン(c-Si)が最適な材料であると考えられる。しかしながら従来の Si プロセスは約 1000 °C の高温処理が必要であり、プラスチック基板上での形成は非常に困難である。本研究室では、メニスカス力を用いた中空構造 SOI(Silicon on Insulator)層の低温転写に取り組んでおり、フレキシブル基板の耐熱温度以下で SOI 層を転写し n チャネル薄膜トランジスタ(TFT)の作製・動作が可能であることを報告している (Meniscus Force Mediated Layer Transfer: MLT)。[2] ここで中空構造 SOI 層とは、局所的にSiO2 柱で支えられた c-Si 膜である。これまでの問題点として n チャネル及び p チャネルパターンの同時転写が為されていない事が挙げられる。よって本研究では MLT 技術を用いた CMOS 回路作製プロセスの構築を試みた。

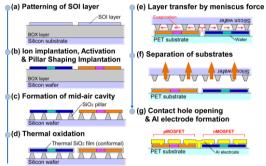

実験方法>SOI 基板[SOI 層: p-type Si(100), 8-20  $\Omega$ ·cm]を、 $1 \mu m \times 6 \mu m$  のライン両端に  $15 \mu m \times 15 \mu m$  の井桁を配置したドッグボーン形状にパターニングした(Fig.1.(a))。ここでチャネル、ソース、ドレイン領域を形成するためにイオン注入法により不純物ドーピングし、活性化アニールを行った(Fig.1.(b))。その後、SiO2 柱の形状制御のために追加のイオン注入(Pillar Shaping Implantation: PSI)を  $P^+$ :  $1 \times 10^{14}$  /cm², 130 keV の条件で行い、BOX 層(SiO2層)を 25% の HF(30 °C)にてエッチングすることで中空構造 SOI 層を形成した(Fig.1.(c))。PSI の導入により SOI/BOX 層界面付近の BOX層にダメージが与えられエッチングレートが増加することで、パターン直下の SiO2 柱の形状がテーパー形状に制御可能となる。次に中空構造を保持した状態で熱酸化した後(Fig.1.(d))、中空構造 SOI 層とポリエチレンテレフタレート

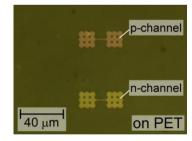

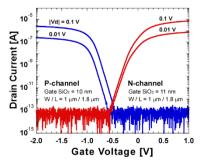

(PET)基板を水を介して対向密着させ 80 °C のホットプレート上で水 分を蒸発させることで基板間に強いメニスカス力を誘起させ (Fig.1.(e))、その後、基板を分離することで SOI 層を PET 基板へ転写し た(Fig.1.(f))。最後にコンタクトホール形成、A1配線を行った(Fig.1.(g))。 以上のプロセスにおいて、PET 基板上での最高温度は 130 °C である。 **結果>**本研究で導入した PSI は高加速エネルギー(130 keV)で実施する とで SOI 層内での P<sup>+</sup>の散乱を抑制し SOI 層の欠陥を低減させ、効率 良く BOX 層にダメージを与える事が可能となる。結果としてnチャネ ル及び p チャネルパターンの PET 基板上への同時転写に初めて成功し た(Fig. 2.)。Figure 2 より元の位置・形状を維持し、かつダメージの無 いパターンが転写されていることが分かる。上述のプロセスで作製し た n チャネル及び p チャネル TFT の I<sub>d</sub>-V<sub>g</sub> 特性を Fig.3 に示す。Fig. 3 より各 TFT は電界効果移動度はそれぞれ 529 cm<sup>2</sup>/Vs (n), 191 cm<sup>2</sup>/Vs (p) を示している。これらに加え PET 基板上に作製した CMOS インバータ は入力に対し明瞭な反転出力を示し、5段 CMOS リングオシレータは 電源電圧 7V において発振周波数 14.3 MHz の高速動作を実現した。

以上より本技術を応用することで、プラスチック基板上において多種多様な材料の電子デバイスと c-Si CMOS 回路とのハイブリッドが実現でき、フレキシブルエレクトロニクスの更なる発展が期待できる。**謝辞**>本研究の一部は広島大学ナノデバイス・バイオ融合科学研究所(RNBS)の施設を用いて行われた。*References*: [1] H. Cheong, K. Kuribara, S. Ogura, N. Fukuda, M. Yoshida. H. Ushijima, and S. Uemura, Jpn. J. Appl. Phys. **55**, 04EL04 (2016). [2] K. Sakaike, M.Akazawa, S. Nakamura, and S. Higashi, Appl. Phys. Lett., **103**, 233510 (2013).

**Fig. 1** Schematic diagram of CMOS process by meniscus force mediated layer transfer technique.

**Fig. 2** Optical microscope image of transferred SOI patterns on PET.

**Fig. 3** Transfer characteristics of n- and p-channel TFTs on PET.