### スパッタエピタキシー法で作製した高電流密度の Si/SiGe 正孔トンネル型 RTD

# Si/SiGe hole-tunneling RTD with high-current density formed

## by sputter epitaxy

東京農工大院工, <sup>○</sup>脇谷実, 塚本貴広, 須田良幸 Tokyo Univ. of Agric. & Technol., <sup>○</sup>M. Wakiya, T. Tsukamoto, and Y. Suda e-mail:sudayos@cc.tuat.ac.jp

## 【研究背景・目的】

#### 【実験方法および結果】

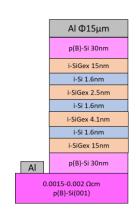

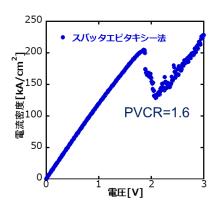

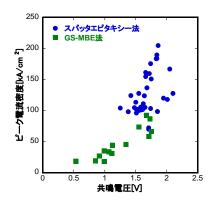

図1に GS-MBE 法とスパッタエピタキシー法で成膜した素子構造を示す。図1より、p-Si 薄膜のそれぞれのドーパント濃度は  $7.7\times10^{18}$ cm<sup>-3</sup> 及び  $2.1\times10^{19}$ cm<sup>-3</sup> で、各成膜法の成膜温度はそれぞれ  $600^{\circ}$ C及び  $530^{\circ}$ C、素子のメサ面積は直径  $15\,\mu$  m である。スパッタエピタキシー法で作製した素子の最高ピーク電流密度は 204kA/cm² となり、GS-MBE 法と比較して約 2.8 倍になったが、PVCR(山対谷電流比)は同程度であった。また、各成膜法による表面荒れ(Rms 値)はそれぞれ 0.27nm 及び 0.67nm となった。スパッタエピタキシー法を用いた素子の電流密度が向上した要因は、ドーパント濃度の増加によるものだと考えられるが、高い Rms 値によって量子井戸部の透過率が減少したことで PVCR は増加しなかったと考えられる。以上の結果から、スパッタエピタキシー法を用いた素子の平坦性は、GS-MBE 法の素子より若干低い値であったが、スパッタエピタキシー法を用いて同程度の PVCR をもつ高ピーク電流密度の完全歪 p-RTD の作製に成功した。

図1比較した本素子図2スパッタエピタキシー法で作製し図3の構造た典型的な p-RTD 電流-電圧特性

図3 各成膜法とピーク電流密度との関係

#### 参考文献

1) H. Maekawa, Y. Sano, C. Ueno, and Y. Suda, J. Crystal Growth **301-302**, 1017 (2007). 2) H. Hanafusa, N. Hirose, A. Kasamatsu, T. Mimura, T. Matsui, H. M. H. Chong, H. Mizuta, and Y. Suda, Appl. Phys. Express **4** (2011) 024102. 3) T. Okubo, T. Tsukamoto, and Y. Suda, Appl. Phys. Express **7** (2014) 034001.