## SOI ピクセル検出器高感度化に向けた TCAD シミュレーション

Simulation study of SOI pixel detector based on linear mode avalanche photodiode

総研大¹, 高エネ研² ○(D)浜崎 竜太郎¹, 新井 康夫²

SOKENDAI<sup>1</sup>, KEK IPNS.<sup>2</sup>, °Ryutaro Hamasaki<sup>1</sup>, Yasuo Arai<sup>2</sup>

E-mail: ryutaro@post.kek.jp

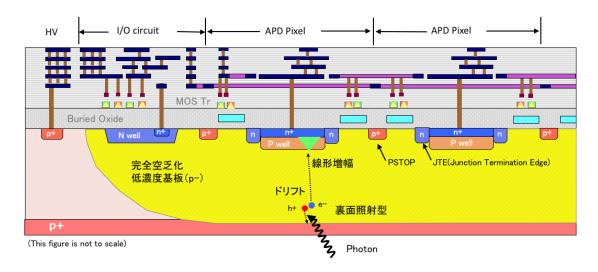

近年、Silicon On Insulator (SOI) 技術を用いて、埋め込み酸化膜(SiO2~200nm 厚)下部の支持基板 (50-500  $\mu$  m 厚)にフォトダイオードを形成し、上部に信号読み出し回路を実装したモノリシック型の X線 CMOS イメージセンサである SOI ピクセル検出器 [1]が注目されている。本研究ではこの SOI ピクセル検出器を軟 X線検出用途に適した構造の研究開発を行っている。軟 X線は物質に対する透過能が低いため裏面入射型を採用し、また生成キャリア数が少ないためセンサ部に内部利得を持たせた Avalanche Photodiode(APD)を使用する。ただし、APD の動作モードにおいては SiPM などのガイガーモード(増幅率 M~10 $^5$ -10 $^6$  倍程度)ではなく低ノイズでアナログ線形素子であるリニアモード (増幅率 M~10-100 倍程度) 駆動をさせることにより、位置・時間・エネルギーを同時に測定を行う。また本研究では軟 X線直接検出のため Reach Through(RT)型 APD(N+/PWell/Psub/P+) [2]について考察する。RT 構造において、印加電圧を調整し、完全空乏化した際に表面の増倍領域で均一なアバランシェ臨界電界にする必要があり、特にエッジ部において不均一な電界構造を抑制するために Edge Termination 法(Guard Ring, Junction Termination) [3]が効果的である。本講演では TCAD シミュレーションによるこれらの構造の電気的特性について報告する。

Fig1.Cross section of RT-SOIAPD

- [1] Y.Arai et al.," Development of SOI pixel process technology "NIMA, 636 (2011), p.31

- [2] T.Kaneda et al., "A model for reach-through avalanche photodiodes "JAP47,3135 (1976)

- [3] G.Pellegrini et al.," Technology developments and first measurements of Low Gain Avalanche Detectors (LGAD) for high energy physics applications" NIMA, 765 (2014), p.12