## AOFP 回路を用いた 16-word×4-bit レジスタファイルの設計と評価

Design and evaluation of a 16-word by 4-bit register file using AQFP logic 横国大院工 <sup>1</sup>,横国大 IAS<sup>2</sup>,JST さきがけ <sup>3</sup>

°(M1)野副 舞 <sup>1</sup>,竹内 尚輝 <sup>2,3</sup>,Christopher Ayala<sup>2</sup>,山梨 裕希 <sup>1,2</sup>,吉川 信行 <sup>1,2</sup> Dept. of Electrical and Computer Eng., Yokohama Natl. Univ. <sup>1</sup>,

IAS, Yokohama Natl. Univ.<sup>2</sup>, JST-PRESTO<sup>3</sup>

°Mai Nozoe<sup>1</sup>, Naoki Takeuchi<sup>2,3</sup>, Christopher Ayala<sup>2</sup>, Yuki Yamanashi<sup>1,2</sup>, Nobuyuki Yoshikawa<sup>1,2</sup> E-mail: nozoe-mai-dz@ynu.jp

近年、情報機器を構成している半導体 CMOS 集積回路は、消費電力の増大や微細加工技術の限界といった問題により性能の限界が近づいている。そこで、半導体に代わるエネルギー効率の高いデバイスが望まれる。我々は、超伝導集積回路の中でも低消費電力性に優れた断熱型量子磁束パラメトロン(Adiabatic Quantum Flux Parametron; AQFP)回路の研究を行っている。AQFP 回路は回路のポテンシャルを断熱的に変化させることにより CMOS 回路に比べ6桁程度低い消費電力を実現することができる[1]。

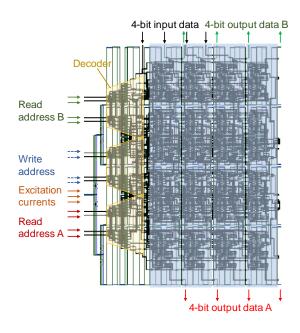

我々は AQFP 回路を用いた超低電力マイクロプロセ ッサの実現に向けて、レジスタファイルの開発を進め ている。レジスタファイルはマイクロプロセッサの重 要な構成要素の1つであり、演算に必要なデータを一 時的に保持する役割を持つ。これまでに AIST 10 kA/cm<sup>2</sup> Nb high-speed standard process (HSTP) を用いて 16-word×1-bit レジスタファイルを設計した。今後、 レジスタファイルの更なる大規模化に向けてビット拡 張性が必要となる。そこで 16-word×4-bit レジスタフ ァイルを設計した。レイアウトを Fig.1 に示す。4 つの 回路ブロックに分割して励起配線を分配することによ り、励起配線による遅延をクロック周波数 5 GHz にお けるタイミングマージン内に収まるように設計した。 回路は 4 phase の励起電流で駆動される。今回の設計 では n+1 番目のビットスライスから読み出されるデー タはn番目から2 phase 遅れて出力される。回路面積 は 5.0×6.5 mm<sup>2</sup>、Josephson 接合数は 5346、5 GHz 動作 時における読み出し動作のレイテンシ (読み出しアド

Fig.1 Layout of a 16-word by 4-bit register file  $\nu$ ス信号が入力されて、1 番目のビットスライスから データが出力されるまでの遅延)は 1450 ps (7.25 クロックサイクル) であった。詳細については発表で報告する。

## 謝辞

本研究に使用された回路は、産業技術総合研究所 (AIST)の超伝導クリーンルーム CRAVITY において HSTP を用いて作製された。本研究は JSPS 科研費基盤 研究(S) (26220904) の助成を受けたものである。

## 参考文献

[1] N. Takeuchi, K. Ehara, K. Inoue, Y. Yamanashi, and N. Yoshikawa, IEEE Trans. Appl. Supercond., vol. 23, no. 3, 1700304, Jun. 2013.