## HVPE 成長 Ga<sub>2</sub>O<sub>3</sub> 膜を用いて作製した Ga<sub>2</sub>O<sub>3</sub> trench MOSFET

Ga<sub>2</sub>O<sub>3</sub> trench MOSFETs fabricated using Ga<sub>2</sub>O<sub>3</sub> films grown by HVPE

ノベルクリスタルテクノロジー1, タムラ製作所2

<sup>○</sup>佐々木 公平<sup>1,2</sup>, ティユ クァン トゥ<sup>1</sup>, 脇本 大樹<sup>1,2</sup>, 小石川 結樹<sup>1,2</sup>, 高塚 章夫<sup>1</sup>, 倉又 朗人<sup>1,2</sup>, 山腰 茂伸<sup>1,2</sup>

Novel Crystal Tech.<sup>1</sup>, Tamura Corp.<sup>2</sup>

°Kohei Sasaki<sup>1, 2</sup>, Quang Tu Thieu<sup>1</sup>, Daiki Wakimoto<sup>1, 2</sup>, Yuki Koishikawa<sup>1, 2</sup>, Akio Takatsuka<sup>1</sup>, Akito Kuramata<sup>1, 2</sup>, and Shigenobu Yamakoshi<sup>1, 2</sup>

E-mail: sasaki@novelcrystal.co.jp

β- $Ga_2O_3$ は 4.5-4.8 eV という大きなバンドギャップを有し、融液成長法によって高品質な単結晶基板を安価に製造できることから、次世代のパワーデバイス用材料として開発が進められている。これまでに、トレンチ MOS 構造を導入した低損失  $Ga_2O_3$  SBD およびトレンチ MOS 型  $Ga_2O_3$  トランジスタの実証に成功していた[1, 2]。今回、プロセス技術とデバイス構造の改良により  $Ga_2O_3$  トランジスタの静特性を改善できたので報告する。

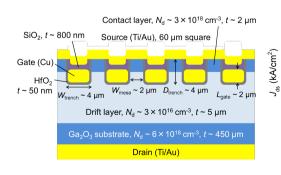

図 1 に試作したデバイスの断面模式図を示す。 $Ga_2O_3$  (001)基板上に、ドリフト層とコンタクト層を HVPE 法で成長した。ゲート絶縁膜には  $HfO_2$  膜を用いた。ゲート電極は Cu、ソース・ドレイン電極は Ti/Au である。ゲート電極とソース電極の分離層には  $SiO_2$  を用いた。素子終端構造やパッシベーション膜は設けていない。デバイス構造の詳細は図 1 を参照頂きたい。

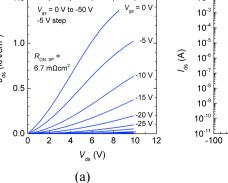

図 2(a)に DC 特性を示す。ドレイン電流密度( $J_{ds}$ )はソース電極の面積から算出した。試作したデバイスは、メサ幅とドナー濃度の関係からノーマリーオン型になっており、ゲート長に対してメサ幅が広いため、ピンチオフ特性が現れない静電誘導トランジスタの特性を示した。ゲート電圧( $V_{gs}$ )が 0V の時の特性オン抵抗( $R_{ON,SP}$ )は  $6.7~m\Omega~cm^2$ であった。 $J_{ds}$ は最大で  $1.36~kA/cm^2$ と大きな値が得られた。図 2(b)に、ドレイン電圧( $V_{ds}$ )が 10 V の時のトランスファー特性を示す。 $V_{gs}$  の増加に伴って単調にドレイン電流( $I_{ds}$ )が減少し、 $10^7$ 以上のオンオフ比が得られた。 $V_{gs}$ が-60 V の時のオフ耐圧は、終端構造等を設けていないため 100 V 程度であった。

本研究の一部は、文部科学省ナノテクノロジープラットフォーム事業 (NIMS 微細加工プラットフォーム)、12025014(F-17-IT-0002)の支援を受けて実施した。

- [1] K. Sasaki, et al.: IEEE Electron Device Lett., 38, 783-785 (2017).

- [2] K. Sasaki, et al.: Appl. Phys. Express, 10, 124201 (2017).

Fig. 1 Schematic illustration of Ga<sub>2</sub>O<sub>3</sub> trench MOSFET.

Fig. 2 (a) DC and (b) transfer characteristics.