## パルススパッタ堆積法による GaN pn 接合ダイオードの作製

Fabrication of GaN pn-junction diodes by pulsed sputtering

○今別府秀行 <sup>1</sup>,上野耕平 <sup>1</sup>,小林篤 <sup>1</sup>,藤岡洋 <sup>1,2</sup>

<sup>1</sup>東大生研, <sup>2</sup>JST-ACCEL

○Hideyuki Imabeppu¹, Kohei Ueno¹, Atsushi Kobayashi¹, Hiroshi Fujioka¹,²

¹IIS, The Univ. of Tokyo, ²JST-ACCEL

E-mail: imabeppu@iis.u-tokyo.ac.jp

【はじめに】次世代パワーデバイス用材料として期待されている GaN は、バルク単結晶基板を用いた 縦型パワーデバイスに関する研究が盛んである。縦型素子の高耐圧化、低抵抗化に向けては結晶中の 不純物濃度の低減や低濃度でのドーピングプロファイルの制御が重要である。これまでに我々のグループではパルススパッタ堆積(PSD)法を用いても、室温電子移動度が  $1000~cm^2V^-ls^{-1}$  を超えるような 低濃度 n型 GaN 薄膜の成長が可能であり[1]、理想係数 1.04 を有する n型 GaN ショットキーダイオードを作製できることを報告した。[2]また PSD 法では成長原料に水素を含まないため、高温の脱水素 アニール処理を施すことなく p型 GaN 薄膜を低温で形成できる。[3,4]さらに成長温度が低いため有機金属気相成長法において顕著になる Mg のメモリー効果や固相熱拡散を抑制でき、急峻なドーピングプロファイルをもった高品質な pn 接合の作製が期待できる。そこで本研究では、PSD 法により縦型 GaN pn 接合ダイオードを作製し、その特性評価を行うことを目的として実験を行った。

【実験方法】 PSD 法を用いて n 型 GaN(0001)基板([Si] =  $2 \times 10^{18}$  cm<sup>-3</sup>)上に Si ドープ GaN、Mg ドープ GaN の順に薄膜を堆積した。フォトリソグラフィおよびドライエッチングを用いて直径 100  $\mu$ m のメサ 構造を形成後、p 型電極として Pd/Ni/Au を、裏面 n 型電極として Ti/Al/Ti/Au を EB 蒸着により堆積し、縦型 GaN pn 接合ダイオードを作製した。尚、本プロセスにおいて、p 型層の活性化アニール処理は行っていない。

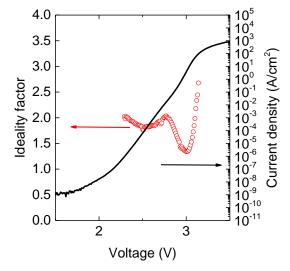

【結果と考察】PSD 法により作製した pn 接合 GaN ダイオードは明瞭な整流性を示し、図 1 に示すような順方向電流電圧特性が得られた。図 1 において印加電圧  $2.2\sim2.8$  V の領域では、理想係数は 2 程度の値が得られ再結合電流が支配的であると解釈できる。 さらに順バイアスを印加すると理想係数が小さくなり、3 V 付近で極小値 1.3 が得られた。この領域では拡散電流が支配的であり、理想的な pn 接合に近い特性が得られたと考えられる。また印加電圧 3.5 V以上の領域において微分抵抗率は 0.2 m $\Omega$ cm²と十分に低い値が得られた。このように PSD 法という低温プロセスを用いても、良好な特性を有する GaN pn 接合ダイオードの作製が可能であることが分かった。

**謝辞**: 本研究の一部は JSPS 科研費 JP16H06414 の助成を 受けて行われたものである。

## 参考文献

- [1]Y. Arakawa et al., Appl. Phys. Lett. 110, 042103 (2017).

- [2] 今別府他、第78回秋季応用物理学会7a-A301-10(2017).

- [3]E. Nakamura et al., Appl. Phys. Lett. 104, 051121 (2014).

- [4]Y. Arakawa et al., APL Mater. 4, 086103 (2016).

Fig.1 Forward I-V characteristics of the GaN p-n junction diode.