## 重イオン放射線に晒された薄膜 BOX-SOI SRAM におけるソフトエラー Soft Errors in Thin-BOX SOI SRAMs Exposed to Heavy Ion Radiation

$\bigcirc$  小林 大輔  $^1$ , 廣瀬 和之  $^1$ , 伊藤 大智  $^2$ , 梯 友哉  $^2$ , 川崎 治  $^2$ , 牧野 高紘  $^3$ , 大島 武  $^3$ ,

松浦 大介 4,成田 貴則 4,加藤 昌浩 4,石井 茂 4,益川 一範 4

(1. JAXA 宇宙研, 2. JAXA 研開, 3. 量研, 4. 三菱重工業 (株))

OD. Kobayashi<sup>1</sup>, K. Hirose<sup>1</sup>, T. Ito<sup>2</sup>, Y. Kakehashi<sup>2</sup>, O. Kawasaki<sup>2</sup>, T. Makino<sup>3</sup>, T. Ohshima<sup>3</sup>, D. Matsuura<sup>4</sup>, T. Narita<sup>4</sup>, M. Kato<sup>4</sup>, S. Ishii<sup>4</sup>, and K. Masukawa<sup>4</sup>

(1. ISAS/JAXA, 2. R&D/JAXA, 3. QST, 4. MHI Ltd.) E-mail: d.kobayashi@isas.jaxa.jp

IoT の実現に向けて集積回路の消費電力削減がいっそう望まれているが,放射線による誤動作「ソフトエラー (SE)」に注意を要する [1]. 通常,消費電力削減に伴って雑音耐性が低下し,より弱い放射線に反応するようになるからである。 SOI 技術は消費電力削減に有利な技術と同時に SE に有利な技術として知られている。近年は埋め込み酸化膜(BOX)を  $10~\rm nm$  程度に薄膜化したものが開発され,更にその下にウェル構造を埋め込み柔軟な基板バイアス( $V_B$ )制御ひいては電力制御を実現するものもある。これについて,正の  $V_B$ (閾値を上げて消費電力を下げる方向を正)を印可した時に SE 耐性が上がった例があり,それは地上の天然放射線(中性子やアルファ線)に対してであった [2,3]。一方,我々は宇宙に存在するような重イオン放射線に対して異なる結果を見出し,その物理を研究している [4,5]。きっかけとなった重イオン放射線試験の結果 [6,7] を報告する。  $10~\rm nm$  薄膜 BOX を持つ SOI SRAM を用いて量研(高崎)で実験を行った。照射前に全てのメ

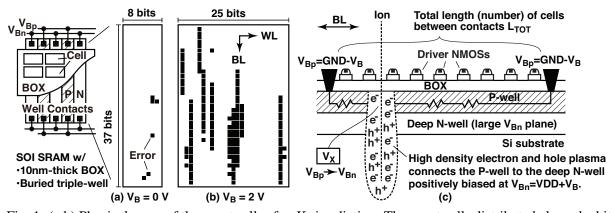

10 nm 薄膜 BOX を持つ SOI SRAM を用いて量研(高崎)で実験を行った。照射前に全てのメモリセルに 0 を書き込み,その状態を保持してサイクロトロン加速器からの重イオンを照射した。その後,読み出して値が変わったセル(SE を起こしたセル)を判別した。なお,照射中は BOX 下のトリプルウェルを利用して  $V_B$  を印可した。Fig. 1 (a,b) に 322-MeV Kr イオン放射線に晒されたメモリアレイの様子を示す。SE を起こしたセル(黒四角)は (a)  $V_B = 0$  V では少数が点状に分布したが,(b)  $V_B = 2$  V では数が多くなりビットライン(BL)に沿って分布した。これは Fig. 1(c) のように,放射線が作った高密度電子正孔対によってトリプルウェルが短絡し,負電位であった Pウェルが正に転じた結果,BOX 上の NMOS トランジスタがオンしたと解釈すると説明できた。

**参考文献** [1] Sengupta, Embedded.com (2014 12/2). [2] Roche, IEDM (2013) p. 766. [3] Zhang, IEEE TNS 63(4), p. 2002, 2016. [4] Chung, 応物秋 (2017) 8a-A411-4. [5] 井辻, 応物秋 (2017) 8a-A411-5. [6] Kobayashi, IRPS (2017) 3D-2. [7] Kobayashi, IEEE TNS 65(1) 2018, to be published.

Fig. 1: (a,b) Physical maps of the upset cells after Kr irradiation. The upset cells distributed along the bit line (BL) direction for a 2-V back bias ( $V_B$ ). (c) Conceptual drawing of the ion strike effect on the buried triple well structure. The struck P-well becomes positive, and NMOS transistors turn on.