## 単層 MoS₂/h-BN/Graphite ヘテロ FET における SS の温度依存性

Temperature dependence of SS in monolayer MoS<sub>2</sub>/h-BN/Graphite hetero-FET 東大工 <sup>1</sup>, 物材機構 <sup>2</sup>, JST-さきがけ <sup>3</sup> ○豊田哲史 <sup>1</sup>, 谷口尚 <sup>2</sup>, 渡邊健司 <sup>2</sup>, 長汐 晃輔 <sup>1,3</sup> UTokyo<sup>1</sup>,NIMS<sup>2</sup>, PRESTO-JST <sup>3</sup> ○S. Toyoda<sup>1</sup>, T. Taniguchi<sup>2</sup>, K. Watanabe<sup>2</sup>, K. Nagashio <sup>1,3</sup> E-mail: toyoda@ncd.t.u-tokyo.ac.jp

## 1. 緒言

h-BN とのヘテロ構造が必須な 2 層グラフェンとは異なり, $MoS_2$ は  $1.9\,eV$  のギャップゆえ,high-k 絶縁膜に存在する荷電不純物による空間的なポテンシャル分布に強く, $10^6$  程度の電流の on/off は容易であることから,既存の半導体プロセスとの適合性が良い.これまでに,high- $k/MoS_2$  の界面準位密度( $D_{it}$ )は,バンドテイル型のエネルギー分布を示すことから, $10^{13}\,cm^2$  程度存在する S 欠陥の準位とは直接的には関係なく,伝導帯を形成する Mo の d 軌道の結合角のゆらぎに起因することを指摘してきた[1]. 起源としては, $SiO_2$  基板表面の粗さや high-k トップゲート堆積により導入された局所歪が要因ではないかと予想される.本研究では原子レベルで平坦な h- $BN/グラファイトバックゲート構造を有する単層 <math>MoS_2$  デバイスを作製し,その輸送特性を精査することで, $MoS_2$  の界面準位の起源を探ることを目標とした.

## 2. 実験方法

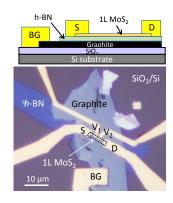

PDMS シート上に h-BN,  $MoS_2$  をそれぞれバルク結晶からテープ転写後, あらかじめ  $SiO_2/Si$  基板に転写しておいたグラファイト上に h-BN, 単層  $MoS_2$  の順で積層した。 PDMS 上での層数判断はラマンにより行った。 最終的に, EB 描画により 4 端子の Ni 電極形成を行い,図 1 に示すデバイスを得た。グラファイトをバックゲート電極として利用することにより  $SiO_2$  基板に存在する荷電不純物の影響を遮断できること,ゲート絶縁膜が 10 nm 厚さの h-BN のみのためゲート容量を大きく取れることが特徴である。

## 3. 結果及び考察

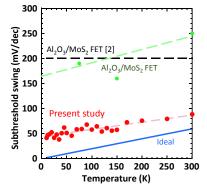

作製したデバイスの室温での 2 端子  $I_{\text{d}}$ - $V_{\text{g}}$  を図 2 に示す。Subthreshold swing(S.S.)は、high-k/MoS<sub>2</sub> FET よりも低い~80 meV/dec を示したことから, $D_{\text{it}}$  が小さいことを示唆している。また,4 端子 $\sigma$ - $V_{\text{g}}$  において,金属/絶縁体転移の挙動を示した。これは,低温でフォノン散乱の抑制による移動度の向上が寄与しており,2 次元界面特性が良好であることを支持している。図 3 に 2 端子  $I_{\text{d}}$ - $V_{\text{g}}$  の S.S.の温度依存性を示す。これまで high-k/MoS<sub>2</sub> FET における S.S.の温度依存性は比較的大きな界面トラップ容量( $C_{\text{it}}$ )の影響のため,温度依存性を示さない[2],もしくは温度依存性が小さいことが多いが,今回のデバイスでは理想に近い温度依存性を示した。以上より,既報の high-k/MoS<sub>2</sub> FET と同じバルク結晶(同じ S 欠陥密度を仮定)から作成した k-BN/MoS<sub>2</sub> へテロ FET において低い S.S.が得られたことから,high-k/MoS<sub>2</sub> で観測されるバンドテイル型の  $D_{\text{it}}$  は,S 欠陥に由来するものでは無く,トップゲート堆積プロセスにより導入されたものであり,プロセス等の改善により向上可能であると示唆される。

**参考文献**[1] N. Fang, *et al.*, J. Phys. D, 2018, (in press). [2] W. Zhu, et al., nature commun., 2014, **5**, 3087. 【謝辞】本研究は科研費及び JSPS「研究拠点形成事業(A.先端拠点形成型)」により助成を受け行われた.

**図1** MoS<sub>2</sub>/h-BN/Gra FET デバイスの光学顕微鏡図及び 断面概念図.

**図2** MoS<sub>2</sub> FET デバイス(2 端子及び4 端子)の輸送特性.

図 3 様々なデバイス構造における S.S.温度依存性.