## ゲートに圧電高分子 P(VDF-TrFE)を用いた FET の静特性評価

Static Characteristics of FET using Piezoelectric Polymer P(VDF-TrFE) for Gate 東京理科大,°(B4)岡山琢哉,(M2)山本堅太郎,宝田隼,古川昭雄

Tokyo Univ. of Science , °Takuya Okayama, Kentaro Yamamoto, Jun Takarada, Akio Furukawa

## E-mail: 7314034@ed.tus.ac.jp

接触センシング技術は、ロボットや透明タッチパッドなど様々な分野で重要な役割を担っている  $^{1)}$ 。本研究は圧力の検出を行うセンサ部と電流への変換を行う FET を同素子内に組み込んだ構造の作製を目的としている。圧力検知膜及び FET のゲート絶縁膜として P(VDF-TrFE)(75/25)を用いた。半導体層には安価で比較的低い温度で成長する ZnO を用いた。

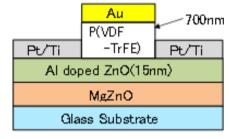

RFマグネトロンスパッタ法により、Fig. 1 のように MgZnO、ZnO:Al、Ti、Pt の積層構造試料を作製した。絶縁膜に用いる P(VDF-TrFE)はスピンコート法により 700 nm 成膜したのちに 135  $^{\circ}$ Cで 2 時間熱処理を行った。ゲート(G)電極に用いる Au は真空蒸着法を用いて成膜した。MgZnO 層は基板と半導体層を絶縁するために成膜している。

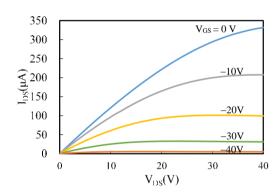

Ti/Pt をソース(S)、ドレイン(D)電極に、Au をゲート電極として用いた。この時のゲート長は 0.5 mm、ゲート幅は 5 mm である。この素子は GS 間に負のバイアスをかけ、SD 間に正のバイアスをかけて作動させるディプレッション型 FET である。この時、 $V_{GS}$  と  $V_{DS}$  を変化させたときの電流-電圧特性を Fig.2 と Fig.3 に示す。

Fig.2 より、ゲートに電圧をかけない状態でもドレイン電圧を大きくすると、 $I_{DS}$ が一定の値に収束する飽和領域が確認できた。また、 $V_{GS}$ を 0 から-40 V と変化させることによって  $I_{DS}$ が小さくなることがわかる。 $V_{GS}=-40$  V の時に半導体層に存在するキャリアを  $3\times10^3$  倍まで減少させることができた。半導体層の厚さ、キャリア濃度、P(VDF-TrFE)の厚さ及び比誘電率をそれぞれ 15 nm、 $2.1\times10^{18}$  cm<sup>-3</sup>、700nm 及び  $6\sim10$  とすると、ゲートの直下にあるキャリアを  $V_{GS}=-40\sim-70$  V で除去できるため、実験結果とおおむね一致している。

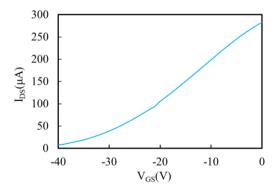

また、 $V_{DS}$  = 40V のときの  $I_{DS}$ - $V_{GS}$  特性を Fig.3 に示す。このグラフの傾きが最大となる点が  $I_{DS}$  の変化量が大きくなる事から接触センシングを行う際に感度が最大となる点である。グラフよりこの時のゲート電圧は約-10 V となる。この時の相互コンダクタンス及びドレイン抵抗はそれぞれ  $10~\mu$ S 及び  $5~M\Omega$ である。よって FET 単体の電圧増幅率は 50 となり、接触センシングに適用可能であると考えられる。

1) R. Dahiya, G. Metta, M. Valle, A. Adami, and L. Lorenzelli: Appl. Phys. Lett. 95, 034105 (2009).

Fig. 1 FET structure.

Fig.2  $I_{DS}$ - $V_{DS}$  characteristics.

Fig. 3  $I_{DS}$ - $V_{GS}$  characteristics.