高周波 CMOS インバータに向けた 4H-SiC トレンチ pMOSFETs の研究

Research on 4H-SiC Trench pMOSFETs for High-Frequency CMOS inverter °井上 純 ¹, 黒木 伸一郎 ¹, 石川 誠治 ¹,², 前田 知徳 ¹,², 瀬崎 洋 ¹,², 牧野 高紘 ³, 大島 武 ³, Mikael Östling⁴, Carl-Mikael Zetterling⁴

1. 広島大学ナノデバイス・バイオ融合科学研究所、2.フェニテックセミコンダクター株式会社、

3. 量子科学技術研究開発機構, 4.KTH Royal Institute of Technology

OJun Inoue<sup>1</sup>, Shin-Ichiro Kuroki<sup>1</sup>, Seiji Ishikawa<sup>1,2</sup>, Tomonori Maeda<sup>1,2</sup>,

Hiroshi Sezaki<sup>1,2</sup>, Takahiro Makino<sup>3</sup>, Takeshi Ohshima<sup>3</sup>, Mikael Östling<sup>4</sup>, Carl-Mikael Zetterling<sup>4</sup>

(1. Hiroshima Univ., Research Inst. of Nanodevice and Bio Systems, 2. Phenitec Semiconductor Co.,Ltd., 3. National Institutes for Quantum and Radiological Science and Technology,

4. KTH Royal Institute of Technology)

E-mail: {inoue-jun, skuroki}@hiroshima-u.ac.jp

【はじめに】4H-SiC は、半導体材料として広く用いられている Si に比べてバンドギャップが大きいという特性 から、高温・高放射線環境などの極限環境でも利用可能な半導体材料として期待されている。本研究グループ では、極限環境でも動作可能な集積回路を実現するため、4H-SiC を材料とした nMOSFET 及び pMOSFET を 作製し、高温および高線量ガンマ線照射後での動作を示した[1,2]。しかし、これらの MOSFET はセルフアラインプロセスではないことからゲート-ソース及びゲート-ドレイン間に大きなオーバーラップ容量が発生し、高 周波駆動が難しくなるといった課題がある。そこで、本研究グループでは nMOSFET の構造をトレンチ型にすることによりオーバーラップ容量を低減する研究を行っている[3]。本研究では、高周波駆動が可能な極限環境 4H-SiC CMOS インバータの実現に向けて、トレンチ型 4H-SiC pMOSFET を作製し動作を確認する研究を行った。

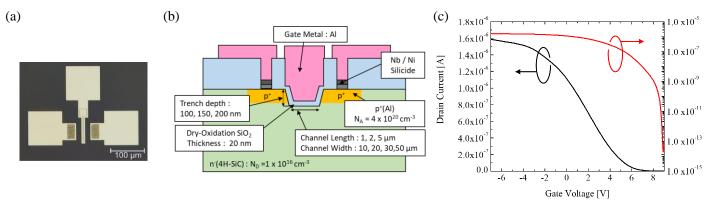

【実験方法】4H-SiC (0001)4°基板上に、 $10 \mu m$  の n 型エピタキシャル層を形成した。不純物は窒素であり、濃度は  $1.0 \times 10^{16} \, \mathrm{cm}^3$  とした。Al イオンを  $500 \, \mathrm{Cm}$  熱下で注入し、不純物濃度が  $4.0 \times 10^{20} \, \mathrm{cm}^3$  の p+ 領域を形成し、カーボンキャップ形成後  $1700 \, \mathrm{Cm}$  での不純物活性化アニールを行った。カーボンキャップ除去後、LPCVD (Low Pressure Chemical Vapor Deposition)で  $\mathrm{SiO}_2$  を堆積した。 $\mathrm{CF}_4$  を用いた RIE (Reactive Ion Etching)で  $\mathrm{SiO}_2$  と  $\mathrm{SiC}$  をエッチングしてトレンチ構造を形成した。 $1150 \, \mathrm{Cm}$  のドライ酸化で  $20 \, \mathrm{cm}$  のゲート絶縁膜を形成後、 $\mathrm{Nb}$  と  $\mathrm{Ni}$  を堆積しアニールを行うことでオーミック電極を形成した。Al をスパッタで堆積させゲート電極とパット電極を形成した。 $\mathrm{LPCVD}$   $\mathrm{SiO}_2$  の堆積により、オーバーラップ容量の低減を狙った。

【測定結果と考察】図 1 に作製したトレンチ型 pMOSFET の写真(a)、構造図(b)、|Id|-Vg 特性(c)を示す。閾値電圧 は 6.0 V、ホール電界効果移動度は 0.88 cm²/Vs、S 値は 233 mV/dec、オンオフ比は  $10^6$  となった。トレンチ深さ が浅かったことにより、チャネル領域のカウンタードープ量が多かったため、閾値が正の値になってしまった と考えられる。

[1] H. Nagatsuma, S-I. Kuroki, M. De Silva, S. Ishikawa, T. Maeda, H. Sezaki, T. Kikkawa, M. Östling, and C.-M. Zetterling, Mat. Sci. Forum, 858, pp573-576 (2016).

[2] J. Kajihara, S.-I. Kuroki, S. Ishikawa, T. Maeda, H. Sezaki, T. Makino, T. Ohshima, M. Ostling, and C.-M. Zetterling, "4H-SiC pMOSFETs with Al-doped S/D and NbNi silicide ohmic contacts, "ICSCRM2017, TH.CP.3. (2017).

[3] T. Kurose, S.-I. Kuroki, S. Ishikawa, T. Maeda, H. Sezaki, T. Makino, T. Ohshima, M. Ostling, and C.-M. Zetterling," Low-parasitic-capacitance self-aligned 4H-SiC nMOSFETs for harsh environment electronics, "ICSCRM2017, WEDP.4. (2017).

図 1. トレンチ型 4H-SiC pMOSFET (a) 光学顕微鏡写真 (b) 構造図 (c) |Id|-Vg 特性 (L=2 μm, W=30 μm)