## ALD 法で形成した Hf0<sub>2</sub>/Ti0<sub>2</sub>/Si0<sub>2</sub> 構造中の界面ダイポール変調

Interface dipole modulation in HfO2/TiO2/SiO2 structures prepared by ALD

産総研<sup>1</sup>, アルバック<sup>2</sup>, ○浅沼 周太郎<sup>1</sup>, 住田 杏子<sup>1</sup>, 宮口 有典<sup>2</sup>, 堀田 和正<sup>2</sup>, 神保 武人<sup>2</sup>, 齋藤 一也<sup>2</sup>, 宮田 典幸<sup>1</sup>

AIST<sup>1</sup>, ULVAC<sup>2</sup>, S. Asanuma<sup>1</sup>, K. Sumita<sup>1</sup>, Y. Miyaguchi<sup>2</sup>, K. Horita<sup>2</sup>, T. Jimbo<sup>2</sup>, K. Saito<sup>2</sup>, and N. Miyata<sup>1</sup> E-mail: shutaro-asanuma@aist.go.jp

HfO<sub>2</sub>をベースとした新規メモリとして界面ダイポール変調 (IDM: interface dipole modulation) が提案されている [1, 2]。これは、 $HfO_2/SiO_2$  界面に 1 分子層程度の Ti 酸化物を入れることで起こる現象で、電界に依存した界面ダイポールの強度変化が観察される。また、MOS 構造に組み込むと、フラッシュメモリのようにしきい値電圧を変化させることができる。一方、これまでの報告例では、酸化膜の堆積に電子線蒸着法が用いられており、半導体量産製造に適した成膜技術での検証が必要であった。本報告では、ALD (atomic layer deposition) 法で作製した  $HfO_2/TiO_2/SiO_2$  積層構造について述べる。

$HfO_2$ 、 $TiO_2$  および  $SiO_2$  膜は、有機金属プレカーサと $O_2$ プラズマを用いた ALD 装置で堆積した。基板温度を 200 Cとし、それぞれの膜を同一成長室内で連続堆積した。なお、 $TiO_2$  変調層の堆積は、4 サイクルとしている。上記の堆積条件で、熱酸化膜を形成した p 型 Si 基板上に  $HfO_2/TiO_2/SiO_2$  積層構造を形成し、 $O_2/Ar$  雰囲気で 300 Cの PDA (post deposition annealing) を施した。また、金電極による MOS キャパシタを作製し、高周波 C-V (capacitance-voltage) 特性を測定した。

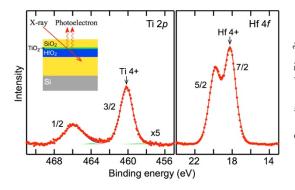

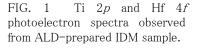

FIG.1 は、 $SiO_2/TiO_2/HfO_2$ 積層構造から観察した x 線励起の光電子スペクトルである。 $HfO_2$  膜中のサブオキサイド成分が極めて少なく、欠陥などは抑制されていると言える。Ti 酸化物のサブオキサイド成分も少なく、 $TiO_2$  が主成分と結論される。また、Ti 2p の光電子強度は Hf 4f に比べて弱く、分子層程度の $TiO_2$  が  $SiO_2/HfO_2$  界面に形成されていると判断される。なお、Ti 酸化物のサブオキサイド成分が増えると、IDM 動作が劣化すると報告されており [3]、ALD の試料でも、この条件は満たしていると言える。実際、FiG 2 に示すように、ALD 作製の MOS キャパシタから IDM 動作を示唆する C-V 特性が得られている。2 層の  $TiO_2$  変調層を含む 試料からは、僅かな時計回りのヒステリシスが観察されている。ここで、蓄積バイアス条件下で基板 Si から酸化膜へホールが注入されたと仮定すると、反時計回りのヒステリシスが起こると予想される。すなわち、観察されたヒステリシスは、キャリア捕獲の影響ではなく、IDM 機構によるポテンシャル変化であると考えられる [1-3]。6 層の  $TiO_2$  層を含む試料からは、さらに広いヒステリシスが観察される。光照射により少数キャリアを生成しながら正バイアスを加えると、負バイアス側へのシフト量がさらに増加している。この結果は、正負両バイアス側で電界による界面ダイポールの変化が起こることを示している。ただし、電子蒸着法による IDM 構造に比べて(約 0.3 V/ 変調層 [3])、変調幅の広がりが小さい。当日は、この違いについて議論する。

- [1] 宮田, 2018 年春季学術講演会, 18p-P7-3 (2018).

- [2] N. Miyata, Sci. Rep. 8, 8486 (2018).

- [3] N. Miyata, Appl. Phys. Lett. 113, 251601 (2018).

FIG. 2 C–V curves of ALD–prepared IDM MOS capacitors. (a) two  ${\rm TiO_2}$  modulation layers and (b) six  ${\rm TiO_2}$  modulation layers.