## Effect of annealing temperature on Al<sub>2</sub>O<sub>3</sub>/NAOS/Si MOS interface properties

## Univ. of Tsukuba <sup>1</sup>, <sup>O</sup> Wei Fu<sup>1</sup>, Xufang Zhang<sup>1</sup>, Hiroshi Umishio<sup>1</sup>, Aboulaye Traore<sup>1</sup>, Hiroshi Yano<sup>1</sup> Takeaki Sakurai<sup>1</sup>

## E-mail: s1730104@u.tsukuba.ac.jp

Aluminum oxide  $(Al_2O_3)$  and Silicon nitride  $(a-SiN_x:H)$  provide an outstanding level of interface passivation on crystalline silicon. An ultrathin SiO<sub>2</sub> layer formed by nitric acid oxidation of Si (NAOS) was used in combination with SiN<sub>x</sub> to improve the interfacial properties of Si solar cells [1]. In order to understand the passivation properties of Al<sub>2</sub>O<sub>3</sub>/NAOS combination layer, in this work, we investigated the influence of post-annealing temperature on the interfacial properties at the Al<sub>2</sub>O<sub>3</sub>/NAOS/Si MOS structure.

A p-type Si (100) wafer with 8~10  $\Omega$  cm resistivity was cleaned using the RCA method, followed by etching with a 5 % hydrofluoric acid (HF) solution to remove the chemical oxide layer. Then, the wafer was immersed in 61wt% HNO<sub>3</sub> solutions at 80 °C for 30 min. The thickness of NAOS SiO<sub>2</sub> layer was estimated to be 1-1.5nm by ellipsometry. Next, 50nm-thick film of Al<sub>2</sub>O<sub>3</sub> was grown by thermal atomic layer deposition (ALD) at temperature of 300 °C on the both sides of the Si substrate with the NAOS layer. After being coated with Al<sub>2</sub>O<sub>3</sub>, the samples were annealed at 450, 500, and 650 °C for 30 min in a N<sub>2</sub> atmosphere. Minority carrier lifetime measurements were obtained by Quasi-Steady-State Photoconductance (QSSPC). The capacitance-voltage (*C-V*) measurements were carried out to characterize the contributions of field-effect and chemical passivation of the NAOS/Al<sub>2</sub>O<sub>3</sub> films.

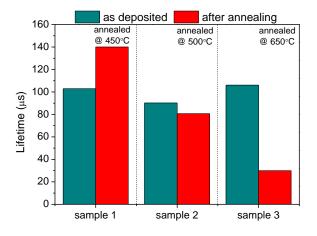

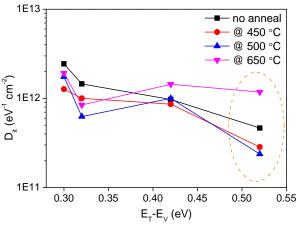

Figure 1 shows the measured carrier lifetimes of Si/NAOS/Al<sub>2</sub>O<sub>3</sub> films annealed at various temperatures. After annealing at 450 °C, the carrier lifetime greatly increases to 140  $\mu$ s, however, for annealing temperature higher than 500 °C, the minority carrier lifetime decreases sharply with increasing of temperature. According to *C-V* measurements, we found out that the samples with the highest lifetime do not correspond to the high fixed charge density. In addition, the interface state density (D<sub>it</sub>) values as a function of energy position are shown in Fig. 2. It is clear that annealing at higher temperatures resulted in higher D<sub>it</sub> values at deep energy levels, whereas for the case without NAOS layer, D<sub>it</sub> values decreases with increasing annealing temperature 450-600 °C[2]. Although the reaction between Al and SiO<sub>2</sub> due to post-annealing can lead to a change of slow states density and oxide fixed charges [3], further investigations have to be performed to inspect the function of these layers on a microscopic scale.

Fig. 1 Comparison of minority carrier lifetime of  $<Al_2O_3/NAOS/Si/Al_2O_3>$  structure without and with annealing treatment performed at 450, 500, and 650°C.

Fig 2 Interface state density  $D_{\rm it}$  as a function of energy position in the silicon bandgap

Mihailetchi, Valentin D., Yuji Komatsu, and L. J. Geerligs. Applied Physics Letters 92.6 (2008): 063510.

Kersten, Friederike, et al. Energy Procedia 38 (2013): 843-848.

[3] Yanase, et al. Electrochemical and Solid-State Letters 13.7 (2010): H253-H256.