# 回路面積を減じた単一磁束量子 NOT ゲートの設計及びエラーレートの評価

Design and error-rate testing of an area-reduced SFQ-NOT gate

# 電通大院 情報理工 <sup>○</sup>山崎洸生, 島田宏, 水柿義直

Univ. of Electro-Comm. K. Yamazaki, H. Shimada, and Y. Mizugaki.

E-mail: yamazaki@w8-7f.ee.uec.ac.jp

### 1. 背景と目的

SFQ 回路はスイッチングの高速性と低消費電力性を活かしたマイクロプロセッサ応用が研究されている[1]。SFQ 回路は大規模化によってクロック配線の複雑化やそれに伴うバイアス電流、回路内磁場の増大が回路動作に悪影響を及ぼす。我々は大規模回路でのクロック配線の単純化、バイアス電流の減少を目的として、SFQ 回路の設計で使われる CONNECT ライブラリ[2]と比較して面積を縮小した論理ゲートの設計に取り組んだ。また、BERはデジタル伝送システムの質を表す重要な指標である。本研究では、設計した省面積論理回路の動作検証とBER の評価を行った。

# 2. 省面積 NOT ゲートの設計

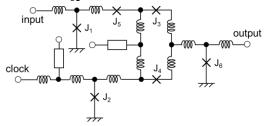

回路面積を縮小した NOT ゲートの等価回路をFig. 1 に示す。input 端子から SFQ が入力されると、J3 がスイッチして J3-J4 ループに SFQ が保持される。J3-J4 ループに SFQ が保持された状態で clock 端子から SFQ が入力されると J4 がスイッチし、保持されていた SFQ は打ち消される。J3-J4 ループに SFQ が保持されていない状態で clock 端子から SFQ が入力されると J6 がスイッチし、output 端子から SFQ が出力される。この回路をセルベースでレイアウト設計を行った。回路面積は 1600μm² で、CONNECT ライブラリの NOT ゲートから 1/4 に縮小されている。

#### 3. 測定結果

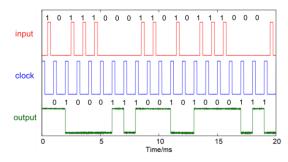

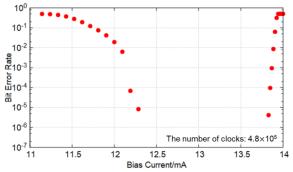

測定は液体 He 中で行った。データジェネレータを用いて疑似ランダムパターンの SFQ パルス列を入力し、オシロスコープでクロック周波数 1kHz の低速測定を行った。低速測定結果の例を Fig. 2に示す。"0"と"1"のそれぞれの入力に対し、clockに対応した正常動作が観測された。データジェネレータを用いて"0"と"1"の交互パターンを入力し、オシロスコープで BER を測定した。BER のバイアス電流依存性を Fig. 3に示す。各測定点においてクロック信号を 4.8×10<sup>5</sup> 回入力し、回路全体のバイアス電流が 12.38mA から 13.81mA の領域では測定でエラーが観測されなかった。

Fig. 1 Area-reduced NOT gate equivalent circuit.

Fig. 2 Waveform example of low-speed testing for the area-reduced NOT gate at 1kHz clock.

Fig. 3 Bias current dependence of the BER at 1MHz clock for the area reduced NOT gate.

# 謝辞

本研究の一部は、JSPS 科研費 17K04979 の助成と、東京大学 VDEC を通した日本ケイデンス株式会社の協力で行われた。本研究に使用された回路は、産業技術総合研究所の超伝導クリーンルーム(CRAVITY)において、STP2 プロセスを用いて作製された。

## 参考文献

- [1] Y. Ando, et. al., IEEE Trans. Appl. Supercond., 26, (2016) 1301205.

- [2] S. Yorozu, et. al., Physica C, 378–381, (2002) 1471–1474.