## 断熱型量子磁東パラメトロン回路を用いた

### 32-word レジスタファイルのビット拡張

# Bit Extension of a 32-word Resister File Using Adiabatic Quantum Flux Parametron Logic

横国大院理工<sup>1</sup>,横国大 IAS<sup>2</sup>

○(M2)田村 智大 <sup>1</sup>, 竹内 尚輝 <sup>2</sup>, Christopher Ayala<sup>2</sup>, 山梨 裕希 <sup>1,2</sup>, 吉川 信行 <sup>1,2</sup>

Dept. of Electrical and Computer Eng., Yokohama Natl. Univ. <sup>1</sup>, IAS, Yokohama Natl. Univ. <sup>2</sup>

○Tomohiro Tamura<sup>1</sup>, Naoki Takeuchi<sup>2</sup>, Christopher Ayala<sup>2</sup>, Yuki Yamanashi<sup>1,2</sup>,

Nobuyuki Yoshikawa<sup>1,2</sup>

#### E-mail: tamura-tomohiro-sz@ynu.jp

現在の情報化社会において主に用いられている CMOS 回路は、消費電力の増大や微細加工技術の限界といった問題から、性能の限界が近づいている。そこで我々は、半導体に代わる新たなデバイスとして、超伝導集積回路技術に基づく断熱型量子磁東パラメトロン (AQFP: Adiabatic Quantum Flux Parametron) 回路の研究を行っている。AQFP 回路は CMOS 回路より消費電力が 5-6 桁ほど少なく、低消費電力性に優れる[1]。

我々は AQFP 回路を用いた超低消費電力のマイクロプロセッサユニット(MPU)の実現に向けて、レジスタファイルの開発を進めている。レジスタファイルは MPU において、演算に必要なデータを一時的に保持する役割を持つ。これまで帰還型の D ラッチを用いた 16-word by 1-bit レジスタファイルが設計されている[2]。先行研究において、16-word by 1-bit レジスタファイルを従来の回路の半分の面積で実現した[3]。

先行研究での最大規模のレジスタファイルは 16-word by 4-bit レジスタファイルである。本研究では、より大規模のレジスタファイルである、32-word by 4-bit レジスタファイルの実現を目的としている。

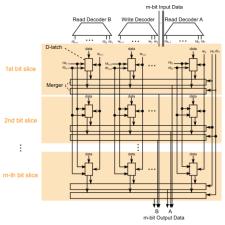

32-word by 1-bit レジスタファイルを設計した結果、32-word に拡張した場合でもチップ内に収めることができることを確認した。そこで、32-word by 4-bit レジスタファイルの実現に向けて、Fig. 1 に示したように 32-word by 1-bit レジスタファイルのビット拡

Fig. 1 Block diagram of a m-word by n-bit register file

張を行った。このビット拡張において、拡張性を持つように設計を行った。また、小型化したレジスタファイルの課題として、ラッチの出力を合流する合流回路の集積度が低いことがあげられるため、合流回路内の空いた面積を有効活用する設計を行った。 謝辞

本研究は JSPS 科研費基盤(A) (19H00760) の助成を受けたものである。

### 参考文献

- [1] N. Takeuchi et al., IEEE Trans. Appl. Supercond., vol. 23, No. 3, 1700304, 2013.

- [2] N. Tsuji et al., IEEE Trans. Appl. Supercond., vol. 27, No. 4, 1300904, 2017.

- [3] 田村他, 金属・セラミックス 超電導機 器合同研究会, 2018 年 12 月