## リセスエッチング後の GaN 表面処理

Surface Treatment of Recess-etched GaN

東芝研究開発センター <sup>○</sup>蔵口 雅彦, 彦坂 年輝, 新留 彩, 梶原 瑛祐, 加藤 大望, 大野 浩志, 向井 章, 布上 真也

Corporate Research & Development Center, Toshiba Corporation

°Masahiko Kuraguchi, Toshiki Hikosaka, Aya Shidome, Yosuke Kajiwara, Daimotsu Kato,

Hiroshi Ono, Akira Mukai, Shinya Nunoue

E-mail: masahiko.kuraguchi@toshiba.co.jp

【はじめに】GaN パワーデバイスにおいて、ノーマリオフ動作を実現するために、ゲート部にエッチングにより、リセス構造を形成する MOS 型デバイスが提案されている。しかし、エッチングに伴うダメージがリセスゲート下のGaN 層に印加されるという課題がある。そこで、ダメージを回復する処理として、アンモニアガスを用いて、結晶性の回復する処理の検討を行い、MOS 型デバイスにおいて、チャネル移動度の増大を確認した結果を報告する。

【実験】Si 基板上に形成された AlGaN/GaN 層に対し、 BCl<sub>3</sub>/Cl<sub>2</sub>ガスによる ICP-RIE を用いて、GaN 層に至るまでエ

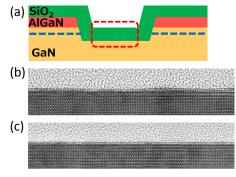

ッチングを行い、リセス構造を形成した。これに対し、アンモニアガスを用いて、熱処理を行った試料と行っていない試料を作製した。各々の試料に対して、断面 TEMによる表面の GaN の結晶性の評価を行うと共に、SiO2 ゲート絶縁膜を形成し、MOS 型デバイスの作製を行った。 MOS デバイスにおいては、電気特性評価からチャネル移動度の解析を行った。

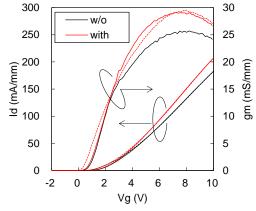

【結果】断面 TEM 像(Fig. 1)からエッチング直後では、表面ラフネスが増大したのに対し、アンモニア処理を行うことで、表面の平坦性が改善した。これは、エッチングによるダメージ層の蒸発、表面再構成が起こったことを示唆する結果と考えている。また、MOS デバイスにおいては、アンモニア熱処理によりドレイン電流と相互コンダク

Fig. 1 (a) Schematic cross-sectional view of the recessed structure. TEM images at the recessed bottom w/o (b) and with (c) surface treatment after recess etching.

Fig. 2. Id-Vg Characteristics of the GaN-MOSFETs of Lg=3um w/o and with surface treatment. The measurement was carried out at Vd=10V.

タンスの増大を確認した(Fig.2)。これにより、チャネル移動度が、118cm2/Vs から 150cm2/Vs までの向上したことを確認した。

## 【参考文献】

1) K. Uesugi et al., Phys. Status Solidi A 2017, 1700511