## Mg<sub>2</sub>Si<sub>1-x</sub>Sn<sub>x</sub> 薄膜の結晶構造及び電気特性の熱処理条件依存性

Effects of post-annealing conditions on crystal structure and electrical properties of

$Mg_2Si_{1-x}Sn_x$  thin films

明大理工¹○布施 翔太郎¹, 勝俣 裕¹

Meiji Univ.1, °Syotaro Fuse1, Hiroshi Katsumata1

E-mail: ce181055@meiji.ac.jp, katumata@meiji.ac.jp

## 【はじめに】

$M_2Si$ の無次元性能指数 (ZT) は900 K付近で0.8~1.0と高く,熱電変換素子への応用が期待されている。しかし, $Mg_2Si$ は熱伝導が高いために,質量差の大きい元素を添加することによって熱伝導率の低減が図られている[1]。 $Mg_2Si_{1-x}Sn_x$ の相図では $0.4 \le x \le 0.6$ で $Mg_2Si$ と $Mg_2Sn$ の複相が得られ三元固溶体が得られにくい。前回,第一原理計算の計算結果より $Mg_2Si$ のSiサイトにSnが置換すると $V_{Mg}$ (Mg空孔)が生成されやすくなり,p型伝導を示すことを報告した[2]。実際に $Mg_ySi_{1-x}Sn_x$ (0 < x < 0.5, 2 > y > 1)三元固溶体薄膜の成膜に成功したが,それらはp型伝導を示した。本研究では, $V_{Mg}$ の生成を抑制するために,共スパッタリング法により成膜した $Mg_2Si_{1-x}Sn_x$ 薄膜の熱処理条件が結晶構造と電気特性に与える影響を評価した。

## 【実験方法】

$Mg_2Si$  ターゲット (3N,  $\phi$ 4 inch) 上に Sn チップ (3N,  $10\times10\times t1$  mm) と Mg チップ (6N,  $5\times5\times t1$  mm) を各々4 枚置き、 $Mg_2Si(Sn)$ ターゲットに対する Mg チップの面積比 ( $Mg/Mg_2Si(Sn)$ ) =0.065 として、共スパッタリング法により c 面サファイア基板および(100)  $CaF_2$  基板上に  $Mg_2Si_{1-x}Sn_x$  薄膜を堆積した。その後、 $Ar/H_2$  (200 sccm) 雰囲気中で 200°C、30 min + 300°C  $\sim$  400 °C、 $1\sim30$  min の二段階熱処理を行い  $Mg_2Si_{1-x}Sn_x$  三元固溶体薄膜を形成した。

## 【結果と考察】

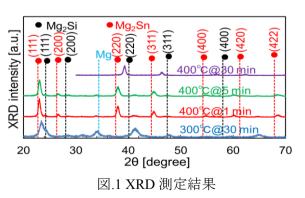

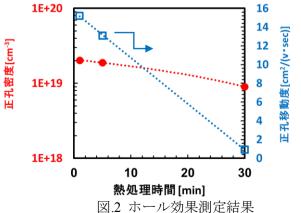

図 1 に XRD 測定結果を示す。400℃、30 min の熱処理後は、Vegard 則より  $Mg_2Si_{0.69}Sn_{0.31}$  の組成が得られることを確認した。400℃、1,5 min の熱処理後は、 $Mg_2Sn$  の生成と孤立 Mg が観測された。300℃、30 min の熱処理後は、 $Mg_2Si_{0.48}Sn_{0.52}$  の形成と孤立 Mg が観測され、 $Mg_2Si_{1-x}Sn_x$  (111) ピークの半値幅は 400℃に比べて増大した。図 2 に 400℃の熱処理時におけるホール効果測定結果の熱処理時間依存性を示す。熱処理時間に関わらず、すべての試料で p 型電気伝導を示した。熱処理時間の増加とともに正孔移動度が低下する要因として、 $Mg_2Si$  の正孔移動度が  $Mg_2Sn$  に比べて低いことが示唆される[3]。

[1] Wei Liu et al., Phys. Rev. Lett. 108, 166601 (2012).

[2] 布施翔太郎他, 第79 応用物理学会秋季学術講演会, 19a-436-6 (2018).

[3] V. K. Zaitsev, et al, Phys. Rev. B 74, 045207 (2006).