# 結晶性酸化物半導体 FET/シリコン FET ハイブリッド構造の 人工ニューラルネットワーク向けアナログ乗算素子の実測結果

A Crystalline Oxide Semiconductor-FET/Si-FET Hybrid Structure-based Multiplier for Artificial Neural Network Applications

(株) 半導体エネルギー研究所 <sup>○</sup>黒川 義元, 青木 健, 上妻 宗広, 木村 肇, 山﨑 舜平

Semiconductor Energy Laboratory Co., Ltd., "Yoshiyuki Kurokawa, Takeshi Aoki, Munehiro

Kozuma, Hajime Kimura, and Shunpei Yamazaki

## E-mail: kurokawa@sel.co.jp

## 【はじめに】

人工ニューラルネットワーク (Artificial Neural Network, ANN) に用いる積和演算をクロスバー方式のアナログ演算で実現する試みが提案されている[1]。アナログ演算を用いることで、演算素子を構成する FET 数の削減、データ信号線数の削減などが期待される。

一方、結晶性酸化物半導体(c-axis aligned crystalline oxide semiconductor, CAAC-OS)をチャネル層とする FET (OS-FET) は、極めて低いオフ電流を示し、電荷保持特性の優れたメモリを構成できることから、プロセッサ、メモリ、FPGA、イメージセンサなど LSI への応用が提案されている[2, 3, 4, 5]。さらに、アナログ電位を保持できることを利用したアナログ乗算素子が提案されている[6]。

本稿では、OS-FET/Si-FET 構造[2, 3, 4]を採用したアナログ乗算素子の基礎特性の実測結果を示し、ANNへの応用可能性を検討する。

## 【OS-FET/Si-FET アナログ乗算素子】

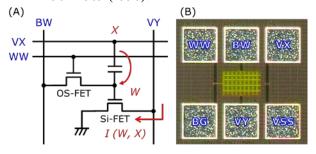

図 1 に試作した OS-FET/Si-FET 構造のアナログ乗算素子の回路構成と光学顕微鏡写真を示す。Si-FET 上に OS-FET を積層している。

図 2 に乗算素子の電流特性の測定結果を示す。測定では、OS-FET を ON として保持容量にデータ W (=  $W_0$  + w)を書込んだ後、OS-FET を OFF として当該データを保持した状態で、信号 VX の電位 X (=  $X_0$  + x)を変化させた際の電流 I (W, X)を計測している。各計測は、異なる W に対して実施している。当該乗算素子には、[1]で必要となるベリファイなどの特別な補正を行わなくても、所望のデータ W に応じ

2.0 図 2. OS-FET / Si-FET 構造のアナログ乗算素子の電流特性の測定結果: 飽和領域では I(W,X) ∞ (W+X-Vth)² で近似できる。 X[V]

た電流Iを取得できるという長所がある。

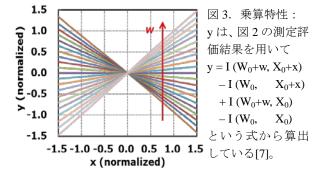

図 3 に、図 2 の測定結果を用いて、4 個の電流から積を取得する方法[7]で算出した乗算特性(重み係数 w、被乗数 x に対して、理想的には  $y = w \times x$  となる)を示す。ここでは、 $W_0 = 2.5V$ 、 $X_0 = 2.5V$  とし、w = 1V、x = 1V の際の電流値で規格化した値を示している。各 w における x と y の相関係数は 0.998 以上であり、 $y = w \times x$  という理想 (相関係数が 1.0) に近い良好な直線性を示している。本特性のアナログ乗算素子は、ANN に応用することができる。

#### 【参考文献】

- [1] R. Mochida et al., VLSI Technology 2018, pp. 175-176.

- [2] Y. Kurokawa et al., ASQED 2013, pp. 66-71.

- [3] T. Aoki et al., ISSCC 2014, pp. 502-503.

- [4] T. Ohmaru et al., ISSCC 2015, pp. 118-119.

- [5] Y. Waseda et al., Mater. Trans. 2018, pp. 1691-1700.

- [6] T. Aoki et al., SSDM 2017, pp. 191-192.

- [7] A. A.- Siddiqi et al., JSSC <u>33</u> (10), pp. 1502-1509 (1998).

図 1. OS-FET / Si-FET ハイブリッド構造アナログ乗 算素子の (A) 回路構成と (B) 光学顕微鏡写真