## 新型超低電圧リテンション FF の提案

Proposal of a new ultralow-voltage-retention Flip-Flop

東工大未来研 瀧口憲一郎, 北形大樹, 松﨑翼, 山本修一郎, 菅原聡

K. Takiguchi, D. Kitagata, T. Matsuzaki, S. Yamamoto, and S. Sugahara, FIRST, Tokyo Inst. of Tech. E-mail: takiguchi.k.ab@m.titech.ac.jp

【はじめに】現在の CMOS ロジックシステムでは、待機時消費電力の削減のためパワーゲーティング(PG)が用いられている[1]. PG のエネルギー削減効率は、ロジックドメイン内の SRAM、FF のデータ保持技術に依存する. FF におけるデータ保持技術には、リテンション FF(R-FF)、Balloon-FF(B-FF)、NV-FF などが提案されている[2-4]. しかし、R-FF では PG 実行時に FF に独立に電源供給を行うため電力削減率が制限され、B-FF ではバックアップラッチへのデータ転送のタイミング制御が煩雑になる. また、NV-FF は不揮発性メモリ素子への書き込みに大きなエネルギーを消費するうえ、プロセスコストが増大する. そこで、我々は CMOS 技術のみで超低電圧(ULV)でリテンションを行い、効果的に待機時消費電力を削減する超低電圧リテンション FF(ULVR-FF)を提案・検討している[5]. 前回までに、ULVR-FF が PG の高効率化に有望であることを示したが、R-FF と比較して面積が増大すること、モード切替の信号制御がやや煩雑であることや、超低電圧リテンション(ULVR)におけるノイズマージンが通常動作時の速度性能とトレードオフになることなどの課題があった. 今回の発表では、省面積で、モード切り替えの信号制御が不要であり、より安定的に ULVR を実現できる新型 ULVR-FF を提案し、その設計方法と回路性能について報告する.

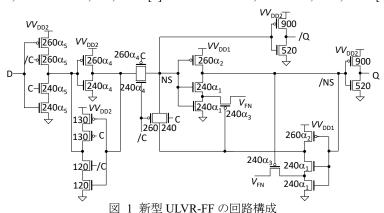

【回路構成】図 1 に新型 ULVR-FF の回路構成を示す. スレーブラッチはデュアルモードインバータで構成され、供給電圧が高いときには通常の双安定回路として高速に動作し(NI モード)、ULV 下でシュミットトリガー双安定回路として機能し安定にデータを保持できる(ST モード). スレーブラッチには 2 本の電源線( $V_{\text{DDH}}$ ,  $V_{\text{DDL}}$ ) からそれぞれに接続されたパワースイッチ(PS)を用いて仮想電源電圧( $V_{\text{DDI}}$ )を生成し、通常の FF 動作には  $V_{\text{DDH}}$ , ULVR 時には  $V_{\text{DDL}}$  の電源供給を行う. マスタラッチについては、通常動作時は  $V_{\text{DDH}}$  の電源線から PS によって  $VV_{\text{DD2}}$ を生成・供給し、ULVR 時は電源を完全に遮断する. 前回報告した ULVR-FF では、フィードバックトランジスタ(FBTr)としてメインインバータのプルアップ側に pMOS を、プルダウン側に nMOS を接続し(cFB型)、通常の FF 動作と ULVR 動作の NI/ST モード切替のために用いる CTRLドライバが必要である[5]. 一方、新型セルはプルダウン側のみに pMOS の FBTr を接続することでトランジスタ数を削減し(pFB型)、また、ULVR のノイズマージンを向上させる. さらに、FBTr に常時  $V_{\text{DDL}}$  を印加することで、CTRLドライバを用いることなく  $VV_{\text{DD}}$  の変化のみで自動的に動作モードの切替が可能になる. 以上から、pFB 型 ULVR-FF は cFB 型よりも省面積で制御も容易になる.

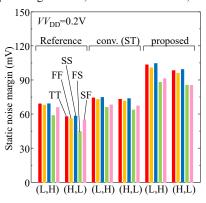

【設計方法と解析結果】解析には HSPICE を用いた. デバイスには 65nm CMOS プロセスの LP モデルを使用し、供給電圧は V<sub>DDH</sub>=1.2V、V<sub>DDL</sub>=0.2V とした. 設計では、スタンダードセルを参考にしたリファレンスセルを基準とし、回路性能を考慮して各 Tr サイズを調整した. ただし、スレーブラッチを構成するデュアルモードインバータは ULVR 時の安定性を確保するためバックワードパス側もフォワードパス側と同じサイズとした. スレーブラッチの設計はトランジスタのバラツキを考慮して、ULVR の SNM が最大となるように設計した. また、速度性能の劣化を抑えつつリーク電力およびセットアップタイムをリファレンスセルと同等となるように設計した. 図 2 にリファレンスセル、cFB 型および pFB 型 ULVR-FF における ULVR 時の SNM を示す. 同図にはスレーブラッチに保持されたデータ(NS、NS)が(H,L)、(L,H)の場合をそれぞれ示している. pFB 型 ULVR-FF は他の構成に比べて高い SNM を確保することができる. pFB 型 ULVR-FF の通常電圧のスタンバイ時のリーク電力はリファレンスセルと同程度であるが、ULVR によってデータを失うことなくスタンバイに比べて 98%程度の電力を削減できる. また、通常動作時の速度劣化も 30%程度に抑えることができる. 面積オーバーヘッドは cFB 型がリファレンスセルに比べて 90%程度であったのに対して、pFB 型では 20%にまで削減できる. 以上から、pFB 型 ULVR-FF は PG に有効であると期待できる.

【謝辞】シミュレーションは東京大学大規模集積システム設計教育センター(VDEC)を通しシノプシス株式会社の協力で行われたものである.

【参考文献】[1]Y. Kanno et al., IEEE JSSC **42**, 74, 2007. [2]V. Zyuban et al., IEEE ISLPED 2002, 98. [3]S. Shigematsu et al., IEEE JSSC **32**, 861, 1997. [4]S. Yamamoto et al., IET EL **47**, 1027, 2011. [5]D. Kitagata et al., IEEE NGCAS 2018, 182.