## 新型超低電圧リテンション SRAM セルの設計と解析

Design and analysis of a new ultralow-voltage-retention SRAM cell

東工大未来研 北形大樹, 吉田隼, 塩津勇作, 山本修一郎, 菅原聡

D. Kitagata, H. Yoshida, Y. Shiotsu, S. Yamamoto, and S. Sugahara, FIRST, Tokyo Inst. of Tech. E-mail: kitagata.d.aa@gmail.com

【はじめに】現在の CMOS ロジックシステムでは待機時消費電力の削減のためパワーゲーティング(PG)が標準的に用いられている[1]. しかし、現状の PG では CMOS ロジック内の記憶回路が揮発性であることに起因して、そのエネルギー削減効率は制約されている. ロジックシステム内の記憶回路の不揮発化は PG の高効率化に有望であるが、不揮発記憶の導入による Break-even time (BET;エネルギーを削減できる最小の電源遮断時間[2])の増大やプロセスコストの増大が課題になる. そこで、我々は不揮発性メモリ素子を用いずに待機時電力を不揮発記憶と同等に削減できる超低電圧リテンション SRAM/FF (ULVR-SRAM/FF) およびこれらを用いた PG の検討を進めている[3,4]. 前回の発表では超低電圧リテンション(ULVR) に重要となるフィードバックトランジスタ(FBTr)を pMOS で構成することで ULVR 時の安定性を大幅に向上できる新型のセル構成と、制御ドライバを用いることなく仮想電源電圧(VVDD)の変化に応じて自動的に動作モード(通常の SRAM 動作/ULVR 動作)を切り替える技術を提案した. 今回はこの新型 ULVR-SRAM セルの詳細な設計方法とその性能について報告する.

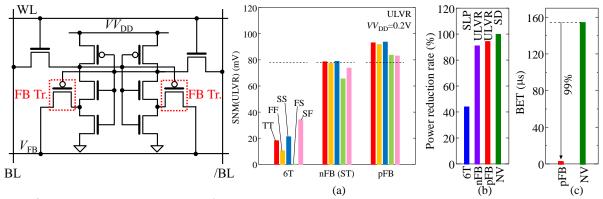

【セル構成】図 1 にヘッダパワースイッチ構成の新型 ULVR-SRAM セルの回路構成を示す. セルはデュアルモードインバータ(DMI)とパストランジスタから構成され, DMI の FBTr.は pMOS で構成し, そのゲート入力は他方のインバータの出力に接続する(以後 pFB セルと呼ぶ). DMI は通常の SRAM 動作時には NI モード(通常のインバータと同等に動作するモード), ULVR 時には ST モード(FB 効果によりリテンションの安定性を向上させるモード)で動作する. FBTr.に常に特定のバイアス( $V_{FB}$ )を加えることで, これらのモードは仮想電源電圧の大きさによって自動的に切り替わる. pFB セルは, nMOS で FBTr.を構成した従来型セル( $v_{FB}$ ) を加えることで, ULVR 時のノイズマージンを大幅に向上できる.

【解析結果】HSPICEを用いてセルの設計と動作解析を行った. デバイスには65nm CMOS プロセスの LP モデルを用いた. ばらつきを考慮したセルの設計方法を確立し、ポストレイアウト解析から寄生抵抗・容量を抽出して、回路性能を評価した. pFB セルおよび nFB セルの通常動作、ULVR にはそれぞれ 1.2V、0.2V の電源線からパワースイッチを介して電力供給を行い、パワースイッチのサイズは、通常動作とULVR のそれぞれのモードにおける SNM を考慮して設計した. 比較用に従来の SRAM セル(6T セル)も準備した. 図 2(a)に 6T セル、nFB セル、pFB セルの ULVR における SNMを示す. pFB セルでは、6T セル、nFB セルと比べて SNM が向上し、わずか 0.2V のリテンションにおいても 80mV を超える SNM が実現できる. 図 2(b)に、6T セルのスタンバイ電力を基準とした、pFB セルのリーク電力削減率を示す. また、同図には 6T セルのスリープ、nFB セルの ULVR、強磁性トンネル接合(MTJ)を用いた NV-SRAM セル[2]の電源遮断におけるリーク電力の削減率も示す. pFB セルは ULVR により 90%以上もの電力を削減できる. この削減率は NV-SRAM セルのリーク電力削減率に匹敵する. 図 2(c)に pFB セルおよび NV-SRAM セルの BET を示す. pFB セルの BET は短く、NV-SRAM セルの BET と比べると 99%も小さい. 以上からpFB セルは高いエネルギー削減効率の PG に応用できると考えられる.

【謝辞】シミュレーションは東京大学大規模集積システム設計教育センター(VDEC)を通しシノプシス株式会社の協力で行われたものである.

【参考文献】[1] Y. Kanno *et al.*, IEEE J. Solid-State Circuits **42**, 2007, 74. [2] D. Kitagata *et al.*, Jpn. J. Appl. Phys. **58**, 2019, SBBB12. [3] D. Kitagata *et al.*, IEEE S3S Conference 2018, paper 13.5. [4] D. Kitagata *et al.*, IEEE NGCAS 2018, pp. 182-185. [5] S. Rusu *et al.*, IEEE ISSCC 2006, pp. 315-324.

図1 新型 ULVR-SRAM(pFB)セルの構成

図 2 (a)ULVR における SNM, (b)リーク電力削減率, (c)BET