## MOS 構造での酸化物ゲート厚さのばらつきと界面準位密度の関連性の考察

Consideration of relationship between the variation of Gate Oxide Thicknesses and the density of interface states for MOS structure Mickael Lozac'h<sup>1</sup>, Sommawan Khumpuang<sup>1,2</sup>, 原史朗<sup>1,2</sup> <sup>1</sup>National Institute of Advanced Industrial Science and Technology (AIST), Device Technology Research Institute, Minimal System Group, Tsukuba, Japan

<sup>2</sup> Minimal Fab Promoting Organization, AIST, Tsukuba, Japan

E-mail: mickael.lozach@aist.go.jp

P-channel metal-oxide-semiconductor field effect transistors (p-MOSFET), also called pMOS, are fabricated by an advanced semiconductor fab: Minimal Fab [1,2]. Minimal Fab is characterized by a modern, cost-effective, fabrication concept [2]. The silicon wafers are minimized to a diameter of 12.5 mm and encapsulated in a shuttle to avoid any contamination, keeping white room condition during the full fabrication process, without the space and budget of a mega fab [2].

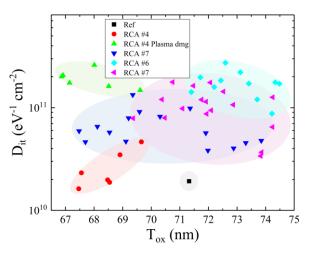

Here, the density of interface state ( $D_{it}$ ) is monitored as a function of the oxide gate thickness ( $T_{ox}$ ) to improve the yield of pMOS devices. The coupled  $D_{it}$  -  $T_{ox}$  variable can improve the reliability of pMOS characterization by underlining the interface Si-SiO<sub>2</sub> quality, which is associated to electrical performance by  $D_{it}$ . For this, we focused on the RCA chemical cleaning, prior to the gate oxide deposition, realized in three different Minimal Fab stations (RCA #4, #6, and #7) with

specific final RCA step HCl/H<sub>2</sub>O<sub>2</sub>/DIW ratio: 1/1/100 and 1/1/6. The gate oxide deposition is then performed at 1150 °C for 50 min by focused light heating. D<sub>it</sub> is calculated about  $10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$  to  $3 \times 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$  from capacitance-voltage measurement at high and quasi-static frequencies [3], and T<sub>ox</sub> is estimated between 67 nm to 74.5 nm from the maximum capacitance oxide. Figure 1 underlines that D<sub>it</sub> - T<sub>ox</sub> can give a precise "identity" of a specific RCA process, and underline possible interface damage due to plasma etching where D<sub>it</sub> about  $3 \times 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$  is observed. An excellent interface quality is obtained with D<sub>it</sub> <  $5 \times 10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$ .

**References:** [1] S. Hara et al., J. Jpn. Soc. Precis. Eng. **77** (2011) 249-253. [2] S. Khumpuang et al., IEEE Trans. Semic. Manuf. **28** (2015) 393-398. [3] A. V. Penumatcha et al., IEEE Trans. Elec. Dev. **60** (2013) 923-926.