## ナノ人工物メトリクスのためのナノ構造埋込 Si MOSFET の試作と評価

Fabrication and characterization of nanostructure-embedded Si MOSFET for nano-artifact-metrics

北大 量集センター<sup>1</sup>, 大日本印刷 <sup>2</sup>, 産総研 <sup>3</sup>, °水野慎太郎 <sup>1</sup>, 呂任鵬 <sup>1</sup>, 清水克真 <sup>1</sup>, 殷翔 <sup>1</sup>, 上羽陽介 <sup>2</sup>, 石川幹雄 <sup>2</sup>, 北村満 <sup>2</sup>, 法元盛久 <sup>3</sup>, 葛西誠也 <sup>1</sup>

RCIQE, Hokkaido Univ.<sup>1</sup>, DNP<sup>2</sup>, AIST<sup>3</sup>, OS. Mizuno<sup>1</sup>, R. Lu<sup>1</sup>, K. Shimizu<sup>1</sup>, X. Yin<sup>1</sup>, Y. Ueba<sup>2</sup>, M. Ishikawa<sup>2</sup>, M. Kitamura<sup>2</sup>, M. Hoga<sup>3</sup>, and S. Kasai<sup>1</sup>

E-mail: mizuno@rciqe.hokudai.ac.jp

## 1. はじめに

物理空間とサイバー空間が融合する環境での安全な認証技術として、人工的に複製不可能な物理的特徴を利用した人工物メトリクスが注目されている。レジスト倒壊現象を利用したナノ人工物メトリクスは高いセキュリティ性能を持つ[1]。課題は微小構造の読出しである。我々はナノ構造を MOSFET のゲート直下に埋め込むことで電気的に識別する方法を提案した[2]。本研究では単一ナノ構造を埋め込んだ Si MOSFET の試作と電気特性評価を行った。

## 2. ナノ構造電気的識別コンセプト

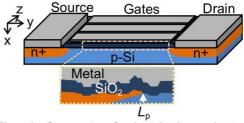

図1に Si MOSFET を用いたナノ構造の電気的読出しのコンセプトを示す。ゲート直下のキャリア分布は埋め込まれたナノ構造の形状によって変化する。チャネル方向の空間分解は、ドレイン電圧をスイープし電流変化を見る。飽和領域においてピンチオフ点  $L_p$  はドレイン電圧に依存することから、ナノ構造の情報を間接的に読み出せる。また幅狭ゲートを複数用意し、ゲートごとにドレイン電圧をスイープすることで横方向分解を行う。

## 3. 実験結果

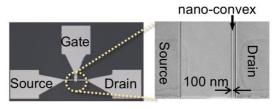

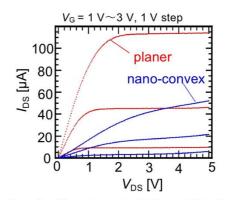

試作した Si MOSFET はチャネル長 12 μm、チャネル幅 6 μm、酸化膜 30 nm である。ドレイン端から 1.4 μm 離れたゲート直下に幅 100 nm、高さ 30 nm のナノ凸構造を埋め込んだ。試作デバイスおよびナノ凸構造の上面図を図 2 に示す。図 3 は試作デバイスの電流-電圧特性である。ナノ凸構造を埋め込んだデバイスでは、凸構造無しのデバイスと比較し線形領域においてオン抵抗が増加するとともに飽和領域でドレインコンダクタンスが増加した。

デバイスシミュレーションより、線形領域で

のオン抵抗増加は凸構造によるチャネルポテンシャルキンクが生じたことが原因である。キンクがキャリアの流れを阻害している。一方、飽和領域でのドレインコンダクタンスの増加は、ドレイン電圧の増加によりポテンシャルキンクが徐々に引き下げられたためである。

本発表内容の一部は NEDO の委託業務 (JPNP16007)の成果である。

- [1] T. Matsumoto et al., Sci. Rep. 4, 6142 (2014).

- [2] K.Shimizu et al., MNC2018, Sapporo, Nov. 2018.

Fig. 1 Concept of electrical readout of nanostructure embedded in MOSFET.

Fig. 2 Top view of fabricated Si MOSFET with a nano-convex.

Fig. 3 *I*<sub>Ds</sub>-*V*<sub>DS</sub> characteristics of fabricated MOSFETs with and without nano-convex.