# 3 次元 TLC NAND 型フラッシュメモリにおける しきい値電圧変調を加えたデータ圧縮方式

Data Compression Technique with  $V_{th}$  Modulation

for 3D TLC NAND Flash Memory

○森 優大, 前田 京佑, 竹内 健 (中大理工)

°Yudai Mori, Kyosuke Maeda and Ken Takeuchi (Chuo Univ.) E-mail: mori@takeuchi-lab.org

### <u>1. はじめに</u>

1セルに3bitを保存するTriple level cell (TLC) NAND型フラッシュメモリでは、8つのしきい値電圧状態を制御しデータを保存する。データ保存時に、隣接するメモリセル間でしきい値電圧が異なることにより電界が発生し、しきい値電圧が変化するエラーが生じる。本論文では、データ保存時に上下のメモリセルのしきい値電圧を近づけるデータ変調を行うことによって信頼性の向上を目指す。また、これと同時にデータ圧縮を行う手法について検討する。

## <u>2.3 次元 TLC NAND 型フラッシュメモリ</u>

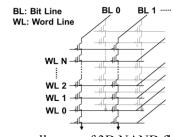

3 次元 NAND 型フラッシュメモリは、Fig. 1 のように、メモリセルを 3 次元に積層することによってメモリセルの高集積化を実現している。TLC NAND 型フラッシュメモリは、1 セルに 3bit を保存する多値化を行うことにより、大容量化を実現している。

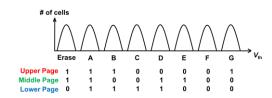

Fig. 2 に TLC NAND 型フラッシュメモリのしきい値電圧分布を示す。多値化を行うことによりしきい値電圧の間隔が狭まる。これにより、本来の保存状態のしきい値電圧に変化が生じた場合、データ読み出し時に他の保存状態として認識してしまうことがある。

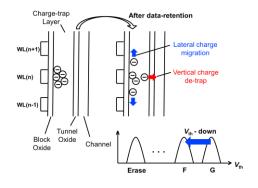

3 次元 NAND 型フラッシュメモリでは、頻繁なデータの書き換えやデータ保存時間によってしきい値電圧が変化するエラーが発生する。Fig. 3 に主なエラーの原因を示す。電子がチャネルに抜け落ちることによってしきい値電圧が低下する現象(Vertical charge de-trap)と電子が隣接するセルに移動する現象(Lateral charge migration)[1]によるエラーがある。

Lateral charge migration はチャージトラップ層を上下のメモリセルと共有する 3 次元 NAND型フラッシュメモリ特有のエラーである。隣接するメモリセルとの電界が大きいほど、Lateral charge migrationの影響は大きくなる。したがって、隣接するメモリセルどうしで保存状態のしきい値電圧を近づけることにより、Lateral charge migrationの影響が抑えられる[2]。

# 3. 結論

隣接するメモリセルとのしきい値電圧を近づける変調によって信頼性が向上すると考え

られる。また、データ変調と同時にデータを圧 縮する手法について検討する。

#### 謝辞

本研究の一部は CREST/JST (グラント番号 JPMJCR1532) の助成により行われた。

### 参考文献

- [1] H.-J. Kang *et al.*, *VLSI Tech.*, June 2015, pp. T182-T183.

- [2] K. Mizoguchi *et al.*, *IEDM Tech. Dig.*, Dec. 2017, pp.19.2.1-19.2.4.

Fig. 1 Memory cell array of 3D NAND flash memory

Fig. 2 V<sub>th</sub> distribution of TLC NAND flash memory

Fig. 3 Error mechanism of 3D NAND flash memory