# 多層電荷蓄積層を有する Hf系 MONOS 型不揮発性メモリの検討

Investigation of Hf-based MONOS nonvolatile memory with multi charge trapping layers

東工大 工学院, O(M2)堀内 勇介, 森田 大貴, 表 柱栄, 大見 俊一郎

Tokyo Institute of Technology, °(M2)Yusuke Horiuchi, Hiroki Morita, Jooyoung Pyo and Shun-ichiro Ohmi

E-mail: horiuchi.y.ac@m.titech.ac.jp, ohmi@ee.e.titech.ac.jp

#### 1. はじめに

前回我々は、Hf 系 MONOS 型不揮発性メモリのデバイス特性について報告した[1]。 今回、Hf 系 MONOS 型不揮発性メモリの電荷蓄積層(CTL)を多層化することによるメモリ特性の向上に関する検討を行ったので報告する[2]。

## 2. 試料作製方法および評価方法

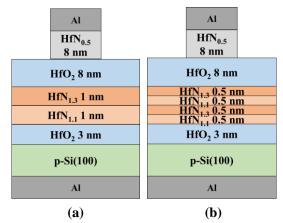

まず、p-Si(100)基板(10-40 Ωcm)を SPM、 DHF で洗浄し、超純水によりリンスを行っ た後、ECR プラズマスパッタ法により MONO( $HfN_{0.5}/HfO_2/HfN_{1.3}/HfN_{1.1}/HfO_2$ ) ゲー ト積層構造を in-situ で形成した。2 層 CTL の場合、トンネル層(TL)として HfO<sub>2</sub> を Ar/O<sub>2</sub>:23/4.6 sccm (0.19 Pa)で堆積し、1 層目  $\mathcal{O}$  CTL(CTL1)  $\mathcal{E}$  L  $\mathcal{T}$  HfN<sub>1.1</sub>  $\mathcal{E}$  Ar/N<sub>2</sub>: 6/6 sccm (0.09 Pa)で、2 層目の CTL(CTL2)として HfN<sub>1.3</sub> を Ar/N<sub>2</sub>: 4/10 sccm (0.096 Pa)で堆積し た。4層CTLの場合は3層目のCTL(CTL3) を CTL1 と、4 層目の CTL(CTL4)を CTL2 と 同様に堆積した。その後ブロック層(BL)を TL と同条件で堆積後、電極(M)として HfN<sub>0.5</sub> を Ar/N<sub>2</sub>:10/0.2 sccm (0.09 Pa)で堆積した。次 に、N<sub>2</sub>雰囲気中で 600°C/1 min の熱処理を行 った。最後に、AI 電極を形成し N<sub>2</sub>/4.9 %H<sub>2</sub> 雰囲気中で 300°C/10 min の熱処理を行い MONOS ダイオードを作製した。図1に作製 した MONOS ダイオードのデバイス構造を 示す。このように作製した試料に関して、 C-V 特性による評価を行った。

## 3. 実験結果および考察

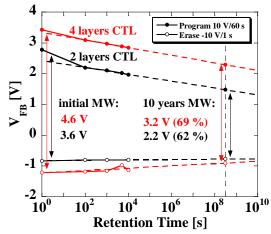

図 2 に CTL を 2 層および 4 層とした場合の Hf 系 MONOS ダイオードの保持特性を示す。 2 層 CTL に対して 4 層 CTL の場合、プログラム電圧 10 V/60 s におけるメモリウィンドウ(MW)が、3.6 V から 4.6 V に増加することが分かった。さらに、CTL を 4 層にすることにより、10 年後の保持率が 62 % から 69 % に増加することが分かった。

#### 謝辞

本研究にご協力いただきました本学の鈴木元也技官ならびに東北大の故大見忠弘名誉教授、後藤哲也教授、黒田理人准教授、諏訪智之准教授、ならびにJSW AFTY の嶋田勝氏、広原正巳氏、玉井逸朗氏に感謝いたします。本研究の一部は、JSPS 科研費 19H00758、東芝デバイス&ストレージ社および文部科学省生体医歯工学共同研究拠点の支援を受けて行われた。

## 参考文献

[1] 工藤 他,第 66 回春季応物予稿集, p.11-091 (2019). [2] Y. Horiuchi, *et al.*, SDM2019, SDM2019-58, pp.25-28 (2019).

図 1 多層 CTL を有する Hf 系 MONOS 構造。(a) 2 層 CTL、(b) 4 層 CTL。

図2保持特性のCTL 堆積層数依存性。