## ニアスレッショルド電圧動作擬似不揮発性 SRAM セルの設計と解析

Design and analysis of virtually nonvolatile SRAM cell for near-threshold voltage operations 東工大未来研 原拓実, 吉田隼, 北形大樹, 山本修一郎, 菅原聡

T. Hara, H. Yoshida, D. Kitagata, S. Yamamoto, and S. Sugahara, FIRST, Tokyo Inst. of Tech. E-mail: hara.t.1011@isl.titech.ac.jp

【はじめに】IoT デバイスに用いるマイクロコントローラ(MC)やシステムオンチップ(SoC)ではその低消費電力化が重要である。このようなロジックシステムに用いる SRAM では、速度性能より低消費電力性能が重要となることから、高しきい値の LSTP デバイスの利用とニアスレッショルド電圧などによる低電圧駆動により待機時電力を削減することが有効である。このような CMOS の低電圧動作では全電力に対する待機時電力の割合が増加することから[1]、低電圧 CMOS においてもパワーゲーティング(PG)は重要になると考えられる。我々は低電圧(0.5V)の SRAM 動作と、超低電圧(ULV:0.2V 程度)を用いたリテンションによって PG を行うことが可能な擬似不揮発性 SRAM(VNR-SRAM)を提案している[2]。今回の発表では、低電圧動作と ULV リテンション(ULVR)の性能向上に有用な新たなセルを提案し、その最適設計と動作解析の結果を報告する。

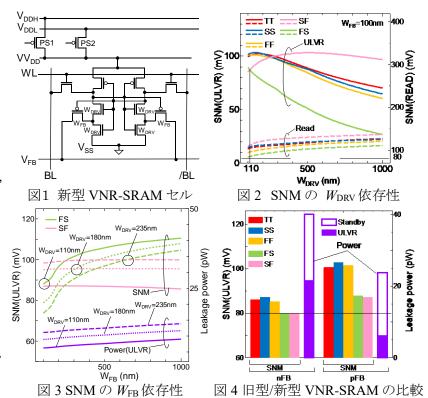

【動作原理】図1に新型の VNR-SRAM セルの構成を示す. セルはデュアルモードインバータ(DMI) [3,4] を用いて構成するが、フィードバックトランジスタ(FBTr)を従来の nMOS から pMOS に変更し、その入力は他方のインバータの出力に接続されている. また、FBTr に一定のバイアス( $V_{\rm FB}$ =0.2V)を加えておくことで、仮想電源電圧( $VV_{\rm DD}$ )の変化によって、ブースト・インバータ(BI)モード( $VV_{\rm DD}$ =0.5V)と、ULVR が可能なシュミットトリガ(ST)モード( $VV_{\rm DD}$ =0.2V)への切り替えが自動的に行われる. 2 種類の電源電圧( $V_{\rm DDH}$ =0.5V、 $V_{\rm DDL}$ =0.2V)から2種類のヘッダパワースイッチ(PS1、PS2)を用いて  $VV_{\rm DD}$ を生成し、セルに供給される. また、ULVR 時の pMOS に基板バイアス効果を発生させリーク電流を削減できるようにセル内のすべてのpMOS のボディを  $V_{\rm DDH}$ に接続した.

【設計方法と結果】HSPICE を用いてセルの設計と解析を行った。デバイスには 65nm CMOS プロセスのLSTP モデルを用いた。新型セルでは FBTr に  $V_{FB}$ =0.2V の一定バイアスを加えているが,このとき通常のSRAM 動作は  $VV_{DD}$ =0.5V の低電圧駆動のため,BI モードでも FB 効果が加わり,SNM を大きくとれる。この低電圧通常動作における SNM のワーストケースは READ 動作であるが,この FB 効果のため,設計の初期値としてドライバ Tr を含めたすべてのトランジスタのサイズは最小サイズ(100nm)とすることができる。図 2 に READ および ULVR 動作における SNM の  $W_{DRV}$  依存性を示す。 $W_{DRV}$  はドライバ Tr のチャネル幅である。フィードバック Tr のチャネル幅  $W_{FB}$  は 100nm とした。READ では  $W_{DRV}$  とともに SNM が増加するが,最小サイズでもすべてのプロセスコーナーで 80mV を超えている。ULVR では  $W_{DRV}$  =110nm で SNM は最大となり,85mV 以上の十分な SNM を確保できる。図 3 に ULVR における SNM とリーク電力の  $W_{FB}$  依存性を示す。図では  $W_{DRV}$ =110,180,235nm の場合を示してある。SNM が最大値(図中の丸で 囲んだ値)となる  $W_{FB}$  は  $W_{DRV}$  に依存し,SNM の最大値は  $W_{FB}$ ,  $W_{DRV}$  の増加とともに大きくなる。ただし,リーク電力は SNM の最大値を大きくすると増加する。図 4 に前回提案および今回提案の VNR-SRAM セ

ルにおける ULVR 時の SNM とリーク電力を示す. 両セルとも最適設計されたセルを用いている. また, 同図には $VV_{DD}$ =0.5Vの待機時電力も示す. 新型セルでは, FB トランジスタを pMOS で構成することにより, SNM の改善と, この基内バイアス効果によるリーク電力はより大きく, リーク電力に特化した設計も可能である.

【謝辞】本研究内容の一部は科研費(基盤 A)の支援を受けた.シミュレーションは東京大学大規模集積システム設計教育センター(VDEC)を通しシノプシス株式会社の協力で行われたものである.

【参考文献】[1] S. Jain et al., IEEE ISSCC, FP 3.6, 2012. [2] 原他,第 80 回応用物理学会秋期学術講演会, 18a-B11-10. [3]D. Kitagata et al., IEEE SNW 2018, p2-17. [4] 吉田他, 第 79 回応用物理学会秋期学術講演会,20a-CE-6,2018.