## First demonstration of (111) Ge-on-insulator n-channel MOSFET fabricated by smart-cut technology

## The University of Tokyo, Faculty of Engineering <sup>1</sup>

## C.-M. Lim<sup>1</sup>, Z. Zhao<sup>1</sup>, K. Sumita<sup>1</sup>, K. Toprasertpong<sup>1</sup>, M. Takenaka<sup>1</sup> and S. Takagi<sup>1</sup>

## E-mail: cmlim@mosfet.t.u-tokyo.ac.jp

**[Background]** A high-performance Ge-on-insulator (GOI) n-channel MOSFET (nMOSFET) is required to establish the Ge CMOS technology [1]. Here, (111) surface orientation has high potential for Ge nMOSFETs because of the low effective mass [2], indicating that (111) GOI nMOSFETs are promising. However, there is no report on the operation of (111) GOI nMOSFETs until now, because of the difficulty in preparing (111) GOI substrates. Recently, we have reported the successful fabrication of (111) GOI wafers by the smart-cut technology [3]. In this work, we demonstrate the operation of (111) GOI nMOSFETs using the GOI substrates fabricated by the smart-cut process. Here, the solid-state diffusion process for  $n^+/p$  junction formation in GOI is examined and optimized.

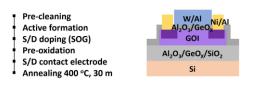

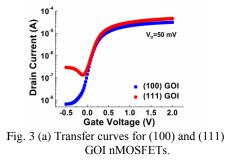

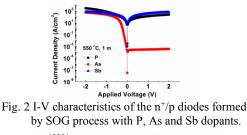

**[Experiments]** The n<sup>+</sup>/p junction diodes were fabricated on bulk Ge wafers by solid-phase diffusion using P-, As- or Sb-doped spin-on-glass (SOG) solutions at 550 °C to establish the S/D junction formation process. This diffusion temperature was chosen, because we have observed that annealing at temperature higher than 600 °C causes critical damages in GOI layers fabricated by the smart-cut process [3]. Using this doping method, we fabricated GOI nMOSFETs on (111) and (100) GOI wafers fabricated by the smart-cut process. Figure 1 shows the fabrication flow and the device structure of the GOI nMOSFETs.

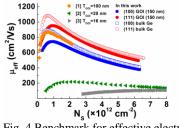

**[Results and discussion]** Figure 2 shows the I-V characteristics of the n<sup>+</sup>/p diodes formed by SOG process with P, As or Sb dopants. Only the As-doped n<sup>+</sup>/p junction shows the high on/off ratio of  $1.6 \times 10^6$  and the excellent ideal factor of 1.02, indicating appropriate diffusion and activation of As atoms at 550 °C. Figure 3 shows the transfer characteristic curves for the fabricated (100) and (111) GOI nMOSFETs. It is observed that the (111) GOI nMOSFET exhibits higher on-current than the (100) one. This is the first demonstration of the operation of nMOSFETs on (111) GOI substrates. Figure 4 shows the benchmark of  $\mu_{eff}$  of GOI nMOSFETs. The present (111) GOI nMOSFET has the highest peak  $\mu_{eff}$  of 951 cm<sup>2</sup>/Vs among the GOI devices and provides the similar mobility behavior to that of fabricated bulk (111) Ge nMOSFETs, confirming the high quality of smart-cut (111) substrates and the superiority of electron transport on (111) Ge substrates.

**[Conclusion]** The well-behaved (111) GOI nMOSFET operation has been demonstrated on the smart-cut (111) GOI substrates by using low-temperature solid-phase As diffusion. The fabricated (111) GOI nMOSFET shows the record high effective mobility of 951 cm<sup>2</sup>/Vs.

**[References]** [1] C. Claeys et al, ECS Trans. **54**, 25 (2013) [2] C. H. Lee et al., IEDM, 1295 (2011) [3] C.-M. Lim et al, Electron Devices Technology and Manufacturing Conference 139 (2019) [4] C. H. Lee et al, Appl. Phys. Lett. **102**, 232107 (2013) [5] W. H Chang et al, IEEE Trans. Electron Devices **64**, 4615 (2017) [6] W. -K. Kim et al, IEEE Trans. Electron Devices **61**, 3379 (2014)

**[Acknowledgments]** This work was supported by JSPS KAKENHI Grant Number 16H06148 and JST-CREST Grant Number JPMJCR1332, Japan.

Fig. 1 Fabrication process and device structure of GOI nMOSFETs

Fig. 4 Benchmark for effective electron mobility of GOI nMOSFETs