## スケーラブル超伝導量子アニーリングマシン開発の現状 - 集積化と実装技術 -

Current states of development of scalable superconducting annealing machines

-Circuit integration and packaging technology-

産総研. 牧瀬 圭正

AIST, Kazumasa Makise

E-mail: kf-makise@aist.go.jp

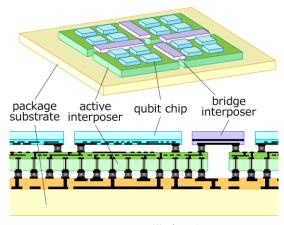

D-waveから超伝導量子ビットによる量子アニーリングマシン商用化され、来年で1 0年目に入る。その間、マシンの高性能化はもちろんのこと、企業への導入、クラウ ドサービスの公開等、着実な進展を見せている。一方でハードウェアの技術課題をい くつか抱えてままである。特に大規模集積化と量子コヒーレンス性能向上は最重要課 題である。集積化に着目すると実用上では100万量子ビット級での集積化が必要とさ れている。磁束量子ビットは絶縁体をトンネル障壁として超伝導で挟んだジョセフソ ン接合からなるSQUID(超伝導量子干渉素子)を基本素子として構成される。しかし SQUIDは半導体のCMOS等と比較すると基本素子の専有面積が大きいことがボトルネッ クとなっている。同様な構造を有するD-waveから今年度に投入が予定されている次世 代アニーリングマシンの "Pegasus" ですら5000量子ビットであり、集積度を上げる ことはそう容易ではない。そこで我々は百万量子ビットを実装可能とするスケーラブ ルな量子アニーリングマシンの実現を目指している。今発表では、スケーラブル量子 アニーリングマシンに向けた超伝導回路の集積化と実装技術の開発の現状について 報告する。図1に100万量子ビット以上を達成するために、産総研で提案した複数のチ ップを一つの基板に搭載したマルチチップモジュール (MCM) を示す。このMCMは 量子ビットとカプラから構成されるQubit chip、その量子ビットの読み出しと制御をつ かさどるactive interposer chipと隣接するチップ間を接続するbridge interposer chip が

同一なpackage substrateに実装される。この 量子ビットを20 mm角チップに敷き詰める と、1チップに62,500量子ビットを集積化 し、16チップ実装すればすることで百万量 子ビットの超伝導量子アニーリングマシ ンを実現することができる。そのために必 要なNb量子ビット集積化技術(超伝導多 層配線集積回路)や三次元実装技術(超伝 導TSV、超伝導フリップチップ接続)の現 状と技術課題について紹介したい。

図1 MCM の構造の断面図