# シミュレーションによるパワーSupply on Chipにおける多層グラフェンの排熱効果の検討

# Numerical investigation of heat removal performance for the multi-layer graphene in power Supply on Chip

九州工大<sup>1</sup>, 産総研<sup>2</sup> 〇(M1) 古江 文乃<sup>1</sup>, 松本 聡<sup>1</sup>, 長谷川 雅考<sup>2</sup>

E-mail: furue.ayano907@mail.kyutech.jp

#### 1. はじめに

Si-LSI やパワーデバイス, 受動部品を1チップに集積したパワーSoC (Supply on Chip) が注目されている[1]. パワーSoC は電源の究極の小型化・高効率化を実現できるが,電源の小型化により発熱密度が増加し,効率低下や短寿命化を引き起こすため排熱技術が重要となる. 多層グラフェンは TIM (Thermal Interface Material)として商品化されており[2], 発熱源である半導体チップへの直接的な実装が効果的であると考えられる. 著者は, 半導体基板と多層グラフェンとの直接接合技術を開発した[3]. 本研究では,多層グラフェンを用いたパワーSoCに適した排熱構造を提案する.

### 2. シミュレーション方法

熱流体シミュレーションを用いて検討した [4]. 境界条件は底面を室温とし、それ以外を断熱とした. GaN パワーデバイスと Si-LSI を集積化することを想定し、主な熱源は負荷である Si-LSI(Si(100))とした. GaN 層はパワーデバイスを想定してサブの熱源とした[5].

#### 3. シミュレーション結果と考察

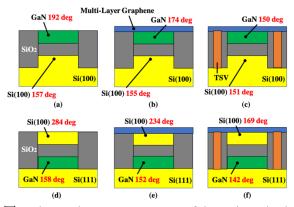

シミュレーション結果を図1に示す. 図1(a) の構造においてメインの熱源 Si(100) が 125 $^{\circ}$ C, サブの熱源 GaN が 100℃になるときの熱量を 求め、全ての構造にそれらの熱量を与えた. 図 1より, Si-LSI の上に GaN を実装する構造 (a) は (d) に比べ発熱部の温度が低い.これは,底 面の境界条件を室温にしているため,メインの 発熱部を底面に近い位置に配置することで排 熱が進んだためと考えられる. 多層グラフェン を使用した構造 (b), (e) は, 使用していない (a), (d) の構造と比べて熱源の温度が下がった. これは水平方向の熱伝導率が 1500W/(m・K)と 非常に高い多層グラフェンを使用することで, 発熱部の熱が水平方向に広がったからである と考えられる. 多層グラフェンを使用した構造 に, TSV (Through Silicon Via) を組み込むと更 なる排熱効果が得られた. TSV の組み込みに より多層グラフェンで水平方向に広げた熱を TSV で上下方向に排熱したと考えられる. 最 も熱源の温度が低かった図1(c) の構造で多層

グラフェンの厚さを変化させたところ,  $2 \mu$  m  $\sim 100 \mu$  m では温度が変わらず, それよりも薄くすると温度が上がった. これは薄くすることで水平方向へ熱が通る断面積が小さくなったからだと考えられる.

## **4.** まとめ

パワーSoC において、GaN パワーデバイス を Si-LSI の上に実装する構造が排熱に適して おり、多層グラフェンと TSV を組み合わせる ことでさらなる排熱効果が得られることを明 らかにした.

$\boxtimes$  1 The maximum temperatures of the main and sub heat source, stacking GaN layer on Si(100) substrate((a),(b), (c)) and stacking Si(100) layer on GaN/Si(111) substrate((d), (e), (f)).

#### 謝辞

本研究の一部は科研費 (18H01430) の助成を受けたものである.

# 参考文献

- [1] T. Phillips, International Workshop on Power Supply on Chip 2018, Session 6-1, 2018.

- [2] A. Tatami, M.Tachibana, T. Yagi, and M. Murakami, 28<sup>th</sup> World Conf. of the Inter. Nuclear Target Develop, Soc.(INTD2016), 2016.

- [3] M. Hasegawa, patent application number, 2018-246592, 2018.

- [4] https://www.muratasoftware.com

- [5] K. Hiura, Y. Ikeda, Y. Hono, and S. Matsumoto, Jpn. J. Appl. Phys, 56, 04CR13, 2017.