## ナノ結晶シリコンを用いた平面型電子放出素子からの電子放出(Ⅱ)

## Electron Emission from Planar-type Electron Source

based on Nanocrystalline Silicon (II)

八戸大工¹, 産総研², 静大電研³ °嶋脇 秀隆¹, 村上 勝久², 長尾 昌善², 三村 秀典³

$Hachinohe\ Inst.\ Technol.\ ^1, AIST\ ^2, Shizuoka\ Univ.\ ^3\ ^\circ Hidetaka\ Shimawaki^1,\ Katsuhisa\ Murakami^2,$

Masayoshi Nagao<sup>2</sup>, Hidenori Mimura<sup>3</sup>

E-mail: simawaki@hi-tech.ac.jp

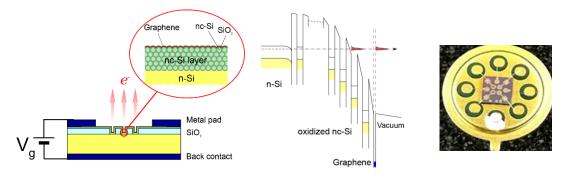

MOS 構造平面型トンネル陰極は、従来の針状構造の電界放射型電子源と比べて、動作電圧が低い、構造がシンプルで再現性が良い、ビーム平行性がよい、低真空動作可能(大気・液中でも)など優れた特長を有する。一方で、電子放出効率(電子取り出し効率)が極めて小さい(1%以下)ことが弱点であり、実用化の妨げとなってきた。電子放出効率が低い主な要因は、基板のフェルミ準位近傍から酸化膜の伝導帯に F-N トンネルした電子が酸化膜と上部電極を走行中に大きな非弾性散乱を受け、大部分の電子が上部電極の仕事関数以下まで走行エネルギーを失うことにある。エネルギー損失抑制には酸化膜および上部電極の薄膜化が有効であるが、各々の薄膜化には限界がある。近年、上部電極として酸化膜上に直接合成したグラフェンを用いた GOS 構造素子からの20%を超える高効率の電子放出が報告され[1]、電極内での散乱抑制に対するグラフェンの有効性が示されると共に、MOS 構造の弱点を克服した理想的な電子源の実現への期待が高まっている。我々は、酸化膜に代わり PLA 法を用いて形成したナノ結晶シリコン膜を用いた平面型電子放出素子を製作し、電子放出特性の評価を行ってきた [2]。これまでに、上部金属電極の薄膜化による電子放出効率の向上は確認できたが、数%に止まっている。本報告では、ナノ結晶系平面型電子源の高効率・高エネルギー化に向けて、ナノ結晶シリコン膜上に直接合成したグラフェン電極を用いた平面型電子放出素子の電子放出素子の電子放出特性、放出電子のエネルギー分布について報告する。

【謝辞】本研究の一部は、科学研究費補助金(No.19K04516)、静岡大学電子工学研究所共同研究の助成によるのもです。

- [1] K. Murakami et al., Appl. Phys. Lett. 114, 213501 (2019).

- [2] H. Shimawaki et al., J. Vac. Sci. Technol. B 26, pp. 864-867, 2008.

Fig. 1 Device structure and optical microscope image