# エピタキシャルリフトオフ(ELO)法による GeOI(111)構造の作成

Fabrication of GeOI(111) structure with Epitaxial Lift Off (ELO) technique 産総研 <sup>1</sup>, 台湾大 <sup>2</sup>, 清華大 <sup>3</sup>, <sup>0</sup>張文馨 <sup>1</sup>, 萬獻文 <sup>2</sup>, 鄭伊婷 <sup>2</sup>, 林延勳 <sup>2</sup>, 入沢寿史 <sup>1</sup>, 石井裕之 <sup>1</sup>, 郭瑞年 <sup>3</sup>, 洪銘輝 <sup>2</sup>, 前田辰郎 <sup>1</sup>

AIST <sup>1</sup>, NTU<sup>2</sup>, NTHU<sup>3</sup> °W. H. Chang <sup>1</sup>, H. W. Wan <sup>2</sup>, Y. T. Cheng <sup>2</sup>, Y. H. G. Lin <sup>2</sup>, T. Irisawa <sup>1</sup>, H. Ishii <sup>1</sup>, J. Kwo <sup>3</sup>, M. Hong <sup>2</sup> and T. Maeda <sup>1</sup>

E-mail: wh-chang@aist.go.jp

### 【背景】

モノリシック 3D CMOS の実現に向け低温で高性能な積層型 CMOS 形成が可能な Geon-Insulator (GeOI)構造が注目されている。我々は、これまでに低温、低ダメージで Ge 単結晶が転写可能な Epitaxial Lift Off (ELO)法にて高品質な GeOI (100)構造を実証してきた[1]。一方、Ge デバイスの性能は面方位に大きく依存することが良く知らされているが[2]、特にGe(111)面は電子移動度が高く、薄膜化による閉じ込め効果も大きく Ge デバイスの性能向上が期待できる。本研究では、ELO 法を用いて良好な GeOI(111)構造の形成に成功したので報告する。

### 【実験方法】

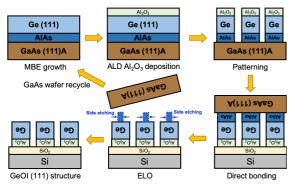

図1にGeOI(111)構造の作成方法を示す。Ge(111)層のドナー基板として、Ge(100nm)/AlAs 構造を GaAs(111)A 基板上に MBE 法にてエピ成長した。貼り合わせする Ge 表面の荒さ改善のため、Ge エピ表面に CMP を施し、さらに ALD-Al<sub>2</sub>O<sub>3</sub> 膜を堆積した。この Al<sub>2</sub>O<sub>3</sub>/Ge/AlAs/GaAs(111)A 構造にパターンを形成後、SiO<sub>2</sub>/Si 基板と 200 度で貼り合わせた。最後に、AlAs 剥離層を HCI により横方向に選択エッチングすることで、Ge(111)層を Si 基板上へ転写した。

Fig. 1. Schematic flow of ELO technique for fabricating Ge(111)OI structures via direct wafer bonding and selective side etching.

## 【結果及び考察】

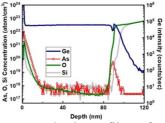

図 2 に GeOI(111)構造の SIMS 分析結果

を示す。Ge, Si と O のシグナルにより、約85 nm の GeOI (111) on Silicon 構造であることがわかる。懸念される Ge 膜中の As 不純物は検出限界かそれ以下であることを確認した。これは MBE 成膜により不純物の混入が抑制されたためである。

Fig. 2. The SIMS depth profiles of As inside Ge(111)OI structures.

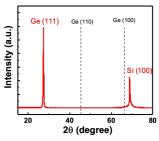

図 3 に GeOI(111)構造の XRD  $2\theta$ スキャンの測定結果を示す。27°と 69°の位置に Ge(111)と Si(100)に起因するピークが観測された。また、測定範囲内(15°-80°)に Ge(100)や Ge(110)に起因するピークが観測されず単結晶 Ge(111)膜の転写に成功していることがわかった。

Fig. 3. XRD  $2\theta$  scan spectra of Ge(111)OI structures, the dashed line indicates the peak positions of Ge (100) and Ge (110), respectively.

#### 【謝辞】

本研究は JSPS 科研費 JP17H06148 と MOST 109-2112-M-002-028、 109-2923-M-002-001、 109-2622-8-002-003 の助成を受けたものです。 【参考文献】

[1] W. H. Chang et al., *IEEE Electron Device Lett.* **37**, 253 (2016). [2] S.-T. Chang et al., *Jpn. J. Appl. Phys.* **47**(**7R**), 5345 (2008).