## 4端子シリコン・エサキダイオードの作製と低温特性評価

Fabrication and low-temperature measurements of 4-terminal Si Esaki diode 静大院工¹,静大電研² ○(M1)金原 涼伽¹,加藤 拓也¹,堀 匡寬¹²,小野 行徳¹²

Shizuoka Univ., °Suzuka Kimpara, Takuya Kato, Masahiro Hori, Yukinori Ono E-mail: kimpara.suzuka.17@shizuoka.ac.jp

## はじめに

我々は、低温における MOS 二次元電子系とフォノンとの相互作用やシリコン中のフォノン伝搬を研究するために、フォノンの出射源(フォノン・エミッター)の開発を進めている。エサキダイオード[1]は、P型半導体とN型半導体の間で起こるトンネル効果(バンド間トンネル)を利用するデバイスであるが、シリコンを基板とする場合、伝導帯電子の谷構造を反映してフォノンアシストによるトンネル電流が支配的となる。このため、バンド間トンネルに際して様々なタイプのフォノンを放出することが知られている[2]。ここでは、放出フォノンのエネルギーの精密計測を目的として、コンタクト抵抗の影響を排除できるクロスブリッジ・ケルビンレジスター構造[3]を応用してエサキダイオードを作製し、フォノン放出に伴う電流変調を観測したので報告する。

# デバイス構造、作製プロセスと測定方法

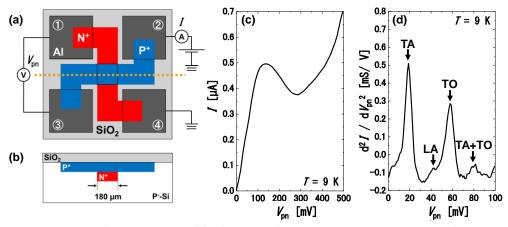

Fig. 1(a), (b)に作製したデバイスの上面図、および断面図(上面図の横点線の部分の断面)を示す。クロスブリッジ構造を有する 4 端子デバイスで、PN 接合面積は 180 x 180  $\mu$ m² である。デバイスは、抵抗率 50  $\Omega$ ·cm の P型(100)面シリコンウエハ上に作製した。高濃度 N型(N+)、および高濃度 P型(P+)領域は、固相拡散により形成した。はじめに PSG 膜からリンを熱拡散させ、続いて BSG 膜からボロンを熱拡散させた。熱拡散の条件はともに 1000  $\mathbb C$ で 10 分である。

測定には、 $N^+$ ,  $P^+$ 領域と Al 電極とのコンタクト抵抗の影響を除去するために、4 端子法を用いた。 $Fig.\ 1(a)$ に示すように、 $N^+$ 端子の一方(図中④の端子)を接地し、 $P^+$ 端子の一方(図中②)に電流 I を印加した時の、端子①③間の電圧  $V_{pn}$  を計測した。

### 測定結果

Fig. 1(c)に、測定温度 T=9 K における  $I-V_{pn}$  特性(順方向特性)を示す。2 端子測定の結果との比較により、 $V_{pn}=\pm0.8$  V の範囲で寄生抵抗は無視できることが判明した(結果不図示)。Fig. 1(d) に I を  $V_{pn}$  で 2 階微分した結果(2 階微分コンダクタンス)を示す。4 個の主たるピーク構造が観測され、エネルギーの低い順に TA フォノン、LA フォノン、TO フォノン、TA+TO フォノンの放出に起因するものと同定された。発表では、フォノン放出に起因するピーク構造の測定温度依存性を含めた詳細を報告する。

本研究は、科研費補助金(Nos. 17H06211, 20K20289, 20H02203, 20H00241)、JST CREST(JPMJCR1774) の助成を受けて行われた。

Fig. 1 Top (a) and cross-sectional (b) views of fabricated device. (c) Current-voltage characteristics measured at 9 K. (d) Second-order differential conductance  $(d^2I/dV_{pn}^2)$ .

#### References

[1] L. Esaki, Phys. Rev. **109**, pp. 603-604 (1958). [2] A. G. Chynoweth et al, Phys. Rev. **125**, pp. 878-880 (1962). [3] N. Stavitski et al, IEEE Trans. Semicond. Manuf. **22**, pp. 146-151 (2009).