# リセスチャネル化によるメタル S/D 型 Ge n-MOSFET の電流駆動力向上

Improvement of current drivability for metal S/D Ge n-MOSFET by introduction of recessed channel structure

## 九大·大学院総合理工学府/研究院, ○(M2)松尾 拓朗, 山本 圭介, 王 冬

IGSES, Kyushu Univ., °Takuro Matsuo, Keisuke Yamamoto, Dong Wang

E-mail: matsuo.takuro.092@s.kyushu-u.ac.jp

## 1. はじめに

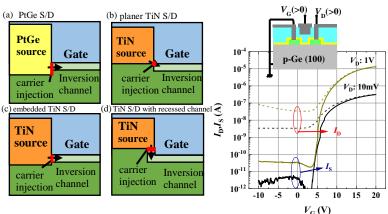

当グループ ではこれまでに、正孔障壁の低い PtGe/Ge コンタクトおよび電子障壁の低い TiN/Ge コンタクトをソース/ドレイン(S/D)とした、メタル S/D型 Ge p-, n-MOSFET を提案してきた[1,2]。 しかし、前者が PN 接合 S/D 型 p-MOSFET 並みのチャネル移動度を示す一方で、後者の電流駆動 力が低いという課題がある。この理由は、反転チャネルと広い面積で接合する PtGe S/D によって 効率の良いキャリア注入がなされる p-MOSFET に対して、反転チャネルと TiN S/D が点(線) 状 でしか接していない n-MOSFET のキャリア注入が効率的に行えず、寄生抵抗が顕在化しているた めと考えている (Fig 1)。実際に、TiN S/D を Ge に埋め込むことでチャネルとの接合面積を増加 させた n-MOSFET では、寄生抵抗の低減と電流駆動力の改善が確認された[3]。一方で、TiN S/D と反転チャネルの接合面積を増加させる手法として、チャネルを掘り込み構造 (リセスチャネル) とする方法も考えられる。本研究では、反応性イオンエッチング(RIE)によってリセスチャネル 構造を形成し、チャネルのエッチング深さと電流駆動力改善・寄生抵抗低減の関係性を包括的に 調査した。

#### 2. 試料作製

p 形 Ge 基板を使用した。基板の化学洗浄後、TiN S/D(60 nm)をスパッタ堆積およびリフトオ フによって形成し、 $350^{\circ}$ C-10 min の PMA を行った。その後、RIE (CHF3 ガスを使用)を用いて、チャネル領域を  $25\sim75$  nm 掘り込み、リセスチャネル構造とした。ゲートスタックには、  $Al/SiO_2/GeO_x$ 構造を使用した。最後にS/Dのコンタクト電極およびバックコンタクトを形成した。 チャネル長 (L) は  $20 \mu m$ 、チャネル幅 (W) は  $20 \mu m$  である。

### 3. 電気特性

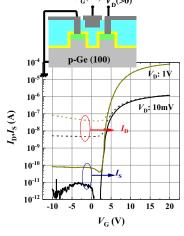

Fig. 2 にプレーナ構造、Fig. 3 に 50 nm のリセスチャネル化を行った n-MOSFET のドレイン電流 およびソース電流-ゲート電圧(Ip. Is-Vg)特性、ならびに当該試料の断面模式図を示す。いずれ も典型的で良好な n-MOSFET の特性が得られている。特にリセスチャネル構造においてはプレ ナ構造に比べて ON 電流が 1 桁大きく、電流駆動力が改善していることが確認できる。これはリセスチャネル化により、TiN/Ge 界面から反転チャネルへの電子の注入効率が改善したためと考え られる。本講演では、寄生抵抗の算出結果やリセスチャネルの深さと電流駆動力との関係性につ いても述べる。

謝辞: 本研究は科研費・基盤研究 (S) (No. 19H05616) および東北大通研共同プロジェクト研究 (No. R03/A02) の支援の下行われた。

参考文献: [1] K. Yamamoto et al., APEX 5, 051301 (2012). [2] Y. Nagatomi, et al., JJAP 54, 070306 (2015). [3] Y. Nagatomi et al., Semicond. Sci. Technol. 32 035001 (2017).  $V_{\rm G}(>0) V_{\rm p}(>0)$

1. Cross sectional illustrations of source/channel contact for various metal S/D MOSFETs.

Fig. 2. Structure and Id, Id-Vg characteristics of n-MOSFET without channel digging.

Fig. 3. Structure and Id, Id-Vg characteristics of n-MOSFET with channel digging.