## MOS 構造におけるゲート酸化物からの Si-0 延伸モードは界面状態の密度と関係があるか? Is the Si-O Stretching Mode from Gate Oxide in MOS Structure related to the Density of Interface States?

Mickael Lozac'h<sup>1</sup>, Sommawan Khumpuang<sup>1,2</sup>, Shiro Hara<sup>1,2</sup>

<sup>1</sup> Minimal Fab Promoting Organization, AIST, Tsukuba, Japan

## <sup>2</sup> National Institute of Advanced Industrial Science and Technology (AIST), Device Technology

Research Institute, Minimal System Group, Tsukuba, Japan

E-mail: mickael.lozach@minimalfab.com

To assess the quality of P-channel metal-oxide-semiconductor field effect transistor (p-MOSFET), also called pMOS, two important parameters are often used: the estimation of the density of interface states between the n-type silicon substrate and the silicon oxide layer, i.e. the gate oxide, and also the quality of the silicon oxide layer itself. The importance to reach the lowest density of interface states (D<sub>it</sub>) is already well established for any semiconductor devices. Here, the optical properties of the silicon oxide are also monitored by Fourier Transform Infra-Red (FTIR) and coupled with the gate oxide process, the chemical cleaning process prior to the gate oxide deposition, and D<sub>it</sub> measured on pMOS devices.

The pMOS devices are fabricated by Minimal Fab [1,2]: an advanced, cost-effective, semiconductor fab where the area of the required cleanroom level is minimized to the surrounding of the silicon wafers (with a diameter of 12.5 mm), encapsulated in a shuttle during the full fabrication process, thus bypassing the space and budget required for a mega fab [2].

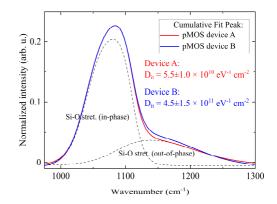

For two pMOS devices A and B realized in a similar process using the same Minimal Fab tools, the  $D_{it}$  is estimated by C-V measurements at  $5.5\pm1.0 \times 10^{10}$  eV<sup>-1</sup> cm<sup>-2</sup> and  $4.5\pm1.5 \times 10^{11}$  eV<sup>-1</sup> cm<sup>-2</sup>, respectively. The Si-O stretching mode, located at the wavenumbers from 1000 cm<sup>-1</sup> to 1250 cm<sup>-1</sup>, and its deconvolution, is shown in **Fig. 1**. The devices are well deconvoluted into two peaks noted in-phase and out-of-phase (**Fig. 1**) [3,4]. Interestingly, the integrated area of the Si-O stretching out-of-phase

is slightly larger for the pMOS device B that also presents a larger D<sub>it</sub>. This could be attributed to some impurities present at the interface and/or some slight damages due to the fabrication process after the high temperature annealing (1150 °C for 1h) for the gate oxide. The nature of such impurity and its concentration or the possible process damages are still under investigation. Besides, the stoichiometry x of the silicon oxide (SiO<sub>x</sub>) can also be determined with the position of the Si-O stretching mode in-phase [3,4]. We estimate a similar stoichiometry about  $1.91\pm0.01$  and  $1.92\pm0.01$  for the pMOS devices A and B, respectively. Thus, coupling the FTIR

analysis with D<sub>it</sub> could be useful for the determination of the Gate oxide quality and its interface with the Si wafer.

References: [1] S. Hara et al., J. Jpn. Soc. Precis. Eng. 77 (2011) 249-253. [2] S. Khumpuang et al., IEEE Trans. Semic. Manuf. 28 (2015) 393-398. [3] E. San Andrés et al., J. Appl. Phys. 87 (2000) 1187-1192. [4] M. Lozac'h et al., Sol. Energy Mater. Sol. Cells 185 (2018) 8-15.