## 半導体レーザの薄膜化プロセスの開発

Process Development of Thinning for Semiconductor Laser Diode 東京理科大学 <sup>1</sup>, **產業技術総合研究所** <sup>2</sup> (M)辻 祐樹 <sup>1</sup>, (M)禹 泰圭 <sup>1</sup>, (M)林 翔平 <sup>1</sup>, 前田 讓治 <sup>1</sup>, 板谷 太郎 <sup>2</sup>, 天野 建 <sup>2</sup>

Tokyo Univ. of Science<sup>1</sup>, AIST<sup>2</sup> Y. Tsuji<sup>1</sup>, T. Woo<sup>1</sup>, S. Lin<sup>1</sup>, J. Maeda<sup>1</sup>, T. Itatani<sup>2</sup> and T. Amano<sup>2</sup>

## E-mail: 7322565@ed.tus.ac.jp

【はじめに】通信サービスの高度化が進展し、大規模なデータセンタにおいて、通信機器の更なる大容量化と省電力化が求められている<sup>(1)</sup>。光接続の更なる高密度実装のために、電子部品と光部品を高度に集積するコパッケージ(CPO: Co-Packaged Optics)技術<sup>(2)</sup>が注目されている。コパッケージ技術は、光源をパッケージの外部に置くか内部に置くかで大別できる。前者は成熟した技術であるが、光ファイバとの結合損が大きく、光源の消費電力が大きくなる傾向がある。後者の場合、発熱源である半導体レーザからの放熱を効果的に行うことが必要である。

我々は、光源内蔵型 CPO 技術の研究開発を行っているが、光源の半導体レーザは、熱伝導率が 0.68 (W/cmK) とシリコンの約半分の InP 基板上に作りこまれている。半導体レーザを薄膜化することで熱容量が小さくなり、放熱領域への熱伝導も増進することから、放熱特性が大幅に向上 すると考えられる。今回、我々は CMP 研磨を用いた半導体レーザの薄膜化プロセスについて報告する。

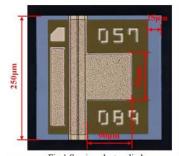

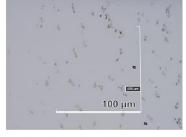

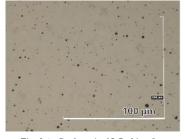

【実験】実験に用いた半導体レーザを図1に示す。発振波長1310 nm の 2.5 Gbps 光伝送用 DFB レーザである。図2に、研磨後の半導体レーザの底面の写真を示す。厚さが  $110\,\mu$  mから、 $60\,\mu$  m以下に研磨されていることが確認された。研磨プロセスとしては、機械式研磨で下部電極を落とした後に、化学的機械研磨 (CMP: Chemical Mechanical Polishing) を行い、機械研磨に起因する欠陥を含む遷移層を除去した。表面観察の結果を図3に示す。溶液を用いた化学エッチと同様な平滑な表面が得られている。その後、AuGe 電極を蒸着して薄膜半導体光源とした。

【まとめ】機械研磨と機械化学研磨を組み合わせることで、表面が鏡面かつ化学的エッチング後 と同等レベルの平滑な表面が得られた。化学研磨によりウェットエッチングと同等のクラックや ~のない表面が得られた。

- (1) 高井厚志「光トランシーバーの Form Factor の新動向 (3)」EE times Japan, 2020/11/16

- (2) NEDO「世界初、光 IC と LSI を一体集積可能とする 3 次元光配線技術を開発」2021/7/2

Fig.1 Semiconductor diode (UNION OPTRONICS CORP, U-CP-1305013p)

Fig. 2 Chemically polished InP chip

Fig. 3 AuGe deposited InP chip after chemical polish

この成果は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の委託業務(JPNP20017)の結果得られたものです。