## AlGaN/GaN MIS-HEMTs におけるパラレル伝導評価 Characterization of parallel conduction for the AlGaN/GaN MIS-HEMTs 北大量集センター

## <sup>○</sup>越智 亮太,橋詰 保,佐藤 威友

Research Center for Integrated Quantum Electronics, Hokkaido Univ.

ORyota Ochi, Tamotsu Hashizume, Taketomo Sato

E-mail: ochi@rciqe.hokudai.ac.jp

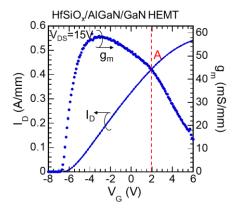

【はじめに】 GaN 系 HEMT は、更なる高速化・高出力化が要請されている。大振幅動作時のゲート漏れ電流制御や経時劣化性の点から、絶縁ゲート構造が望ましい。これまでに、 $HfSiO_x$  を絶縁膜に用いた AlGaN/GaN MOS-HEMT において、非常に低い界面準位や高温での動作安定性が得られることを報告した[1]。しかし、Fig.1 に示す様に、順バイアス( $V_G$ >2V)において電流線形性の劣化( $g_m$  の急激な低下)が生じるという課題がある。これは、順バイアスにおいて、MIS 界面にもチャネルが形成されパラレル伝導が生じる為であると考えられる。MIS 界面での電子移動度はヘテロ界面に比べて低い為に  $g_m$  の低下を引き起こすと考えられる。本研究では、バリア層上により高いバンドギャップを有する 2nd バリア層を追加した HEMT 構造を作製した。これにより、移動度の低いMIS 界面に電子が溜まる前に高移動度が期待されるヘテロ界面にチャネルを形成し、順バイスにおける  $g_m$  の低下を抑制することを試みた。

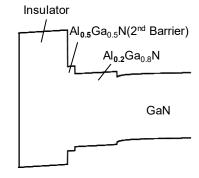

【実験】 Fig.2 に本研究で用いた HEMT 構造のバンド図を示す。 基板には SiC 基板を用いた。バリア層には  $Al_{0.2}Ga_{0.8}N(17nm)$ を用いており、その上に 2nd Barrier 層として  $Al_{0.5}Ga_{0.5}N$  を 3nm 成長した HEMT 構造となっている。まず、ICP-RIE 法を用いて素子間分離を行った。次に、Ti/Al/Ti/Au のオーミック電極を形成し、窒素雰囲気中で 830 の熱処理を行った。その後、 $Al_2O_3$  膜を  $H_2O$  と TMA を原料とした ALD 法により 30nm 堆積した。最後に、Ni/Au のゲート電極を形成した。ゲート長は  $10\mu m$ 、ゲート幅は  $100\mu m$ 、ソース-ゲート・ドレイン-ゲート間隔は  $10\mu m$  である。MOS-HEMT 作成後に  $N_2$  中 300 の PMA 処理を行った[2,3]。また、比較用として  $Al_{0.2}Ga_{0.8}N(20nm)/Ga$  の従来構造においても同様に HEMT も作製し、特性比較を行った。

## 【結果と考察】

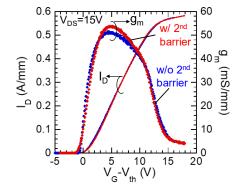

Fig.3 に、MOS-HEMT の伝達特性を示す。比較のためにしきい値電圧を揃えてプロットしている。構造の違いによる伝達特性の振る舞いの差は見られなかった。これは、 $Al_{0.5}Ga_{0.5}N$  層の結晶性が悪く、PMA 後においても高い界面準位密度が存在しており、ゲート電圧に対する電流の制御が阻害されていることが考えられる。この他に、 $2^{nd}$  バリア層とバリア層界面が階段状の界面になっていないことも考えられる。

- [1] R. Ochi et al., AIP Adv. 10, 065215 (2020).

- [2] T. Hashizume et al., Appl. Phys. Express 11, 124102 (2018).

- [3] Y. Ando et al., Appl. Phys. Express 12, 024002 (2019).

**Fig.1** Transfer characteristics of the HfSiO<sub>x</sub>/AlGaN/GaN structure.

**Fig. 2** Band diagram of the MOS-HEMT with 2<sup>nd</sup> Barrier layer.

**Fig. 3** Transfer Characteristics of MOS-HEMTs.