## 紫外光照射による GaN MOS 構造における正孔トラップの評価

Evaluation of Hole Traps in GaN MOS Structures by Ultraviolet Light Illumination 阪大院工<sup>1</sup> <sup>○</sup>富ヶ原 一樹<sup>1</sup>, 中沼 貴澄<sup>1</sup>, 溝端 秀聡<sup>1</sup>, 野﨑 幹人<sup>1</sup>, 小林 拓真<sup>1</sup>, 志村 考功<sup>1</sup>. 渡部 平司<sup>1</sup>

Osaka Univ.<sup>1</sup> °Kazuki Tomigahara<sup>1</sup>, Takato Nakanuma<sup>1</sup>, Hidetoshi Mizobata<sup>1</sup>, Mikito Nozaki<sup>1</sup>, Takuma Kobayashi<sup>1</sup>, Takayoshi Shimura<sup>1</sup>, and Heiji Watanabe<sup>1</sup>

E-mail: tomigahara@ade.prec.eng.osaka-u.ac.jp

【はじめに】低損失 GaN MOSFET の実現に向け、高品質な GaN MOS 界面の形成が不可欠である。これまでに我々は、 $SiO_2$ /GaN 構造に酸素熱処理を施すことで、電子トラップが低減することを報告した[1]. 一方、GaN MOS 界面では正孔伝導が極めて困難であることを指摘しており[2]、正孔トラップの詳細な評価が必要である。本研究では比較的入手が容易な n型 GaN 基板上に MOS キャパシタを作製し、紫外光照射により少数キャリアである正孔を誘起することで、正孔トラップの評価を行ったので報告する。

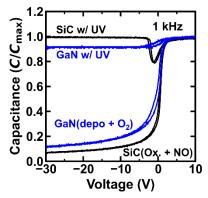

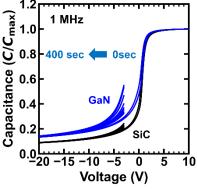

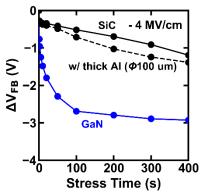

【実験方法・結果】n 型 GaN エピ層 ([Si]: 2.0×10<sup>16</sup> cm<sup>-3</sup>) を 50% HF で洗浄後, プラズマ CVD で SiO<sub>2</sub> 膜を約50 nm 成膜した. 成膜初期には、窒素添加条件でSiON層を約5 nm 形成することで、  $SiO_2$  中への Ga 拡散を抑制した上[3]、800°C、30 分の酸素熱処理を行った. また、比較のために NO 窒化処理を施した SiO<sub>2</sub>/SiC (0001) 試料も用意した. これらの試料に対し, 薄い Ni 表面電極 (厚さ 11 nm, 直径 200 um) を蒸着することで MOS キャパシタを作製した. ここで電極を薄くし たのは、紫外光 ( $\lambda$ : 250 – 450 nm) を電極越しに界面に照射するためである. 図 1 に作製した MOS キャパシタの  $1 \, \text{kHz}$  双方向 C-V 特性 (紫外光有/無) を示す. まず, SiC, GaN のいずれの試料も紫 外光を照射することで,正孔蓄積による負バイアス側での容量増加が確認された. つづいて正孔 トラップ評価のために、紫外光照射下で酸化膜電界-4 MV/cm に対応する負電圧ストレスを印加 し, C-V 特性の変動を観測した. その結果, 図 2 に示すように, ストレス印加に伴い, 膜中トラッ プへの正孔充電による *C-V* 特性の負方向シフトが観測された. 特性の変動は GaN の場合に顕著で あることが分かる. 図 3 にフラットバンド電圧変動 ( $\Delta V_{FB}$ ) をストレス印加時間に対してプロッ トした結果を示す. 図には、比較のために厚い Al 電極 (厚さ 60-70 nm, 直径 100 um) の SiC MOS キャパシタの結果も示す. SiC は間接遷移半導体であるために正孔の再結合寿命が長く, 電極面積 が小さい場合 (直径 100 um) は、紫外光照射により電極周囲に誘起した正孔が電極直下に十分に 供給される[4]. 本研究では薄い Ni 電極を採用して紫外光を電極越しに照射することで, 電極面積 が大きい場合 (直径 200 um) にも十分な正孔を誘起し (図 1),正孔トラップの評価を可能にして いる. 実際に図 3 に示すように, VfB の変動は厚い電極の場合とほぼ整合することが分かる. 方,GaN は直接遷移半導体であるため正孔の再結合寿命が短く,電極周囲から直下に正孔を供給 することは困難である. しかし GaN の場合にも, 薄い電極を採用することで十分な正孔蓄積が確 認され (図 1)、本手法で正孔トラップの評価が可能である. 図 3 に示すように GaN MOS 構造で は  $V_{\text{FB}}$  変動が SiC の場合よりも顕著であり、GaN MOS 構造では正孔トラップが高密度に存在する といえる. 講演当日は成膜条件を変えた場合の比較についても紹介する.

本研究は、文部科学省革新的パワーエレクトロニクス創出基盤技術研究開発事業(JPJ009777)及び科研費(19H00767)の助成を受けた.

- [1] T. Yamada *et al.*, Appl. Phys. Express 11, 015701 (2018). [2] 和田他, 第 82 回 応用物理学会秋季学術講演会, 12p-N305-6 (2021).

- [3] T. Yamada et al., Jpn. J. Appl. Phys. 58, SCCD06 (2019). [4] Y. Katsu, et al., Mater. Sci. Forum 858, 599 (2016).

Fig. 1: Bi-directional *C-V* characteristics of GaN and SiC MOS capacitors with and without UV illumination (frequency: 1 kHz).

Fig. 2: Exemplary *C-V* characteristics obtained during the negative bias stress measurements (frequency: 1 MHz).

Fig. 3:  $\Delta V_{\rm FB}$  as a function of stress time. A stress corresponding to oxide field of -4 MV/cm was applied.