## EID AlGaN/GaN MOS-HEMT のノーマリオフ動作実証

Demonstration of normally-off operation in EID AlGaN/GaN MOS-HEMT

三菱電機株式会社 先端技術総合研究所 1,名古屋工業大学 2

○南條 拓真 1,品川 友宏 1,綿引 達郎 1,三浦 成久 1,江川 孝志 2

Advanced Technology R&D Center, Mitsubishi Electric Corporation<sup>1</sup>, Nagoya Inst. of Tech. <sup>2</sup>

Takuma Nanjo<sup>1</sup>, Tomohiro Shinagawa<sup>1</sup>, Tatsuro Watahiki<sup>1</sup>, Naruhisa Miura<sup>1</sup>, Takashi Egawa<sup>2</sup>

E-mail: Nanjo.Takuma@ap.MitsubishiElectric.co.jp

## はじめに

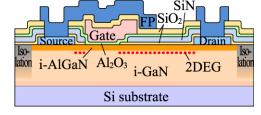

GaN は高周波素子だけではなく、高出力スイッチング素子に用いる半導体材料としても近年注目を集めており、ノーマリオフ動作を実現するためのゲートリセス型 MIS 構造や GIT 構造などが提案されている。しかしながら、これらの構造では半導体表面をドライエッチングする必要があり、そのダメージによる諸特性の劣化が懸念される。本報告では、半導体層をエッチングすることなく 2DEG を選択的に誘起できる EID(Extrinsically electron Induced by Dielectric)構造[1]をドリフト領域に適用した図 1 に示す新規の EID AlGaN/GaN MOS-HEMT を提案する。この構造では、バ

リア層を薄く設計しているためゲート電極直下では 2DEG は誘起されない。一方ゲート電極両側のアクセス領域とドリフト領域には、プラズマ CVD にて SiO<sub>2</sub> 膜を堆積した後に高温熱処理する EID 構造を採用し、これらの領域にのみ選択的に 2DEG を誘起する。これによりノーマリオフ動作が実現される。

Figure 1. Cross-sectional structure of EID-HEMT

## 実 験

EID-HEMT は Si 基板上に成長した AlGaN/GaN エピタキシャル層を用いて作製した。AlGaN 層の Al 組成と厚さはそれぞれ 20%と 5nm とした。作製プロセスは素子分離領域から開始し、その後にソース/ドレイン電極と SiO<sub>2</sub> 膜を堆積し 850°Cにて 30 秒間の熱処理を実施した。これにより ヘテロ界面に 2DEG が誘起される。ゲート電極は、SiO<sub>2</sub> 膜と SiN 膜を BHF にてウェットエッチングした上で、ALD 法にて堆積した  $Al_2O_3$  膜上に形成した。また、図 1 に示すような 3 段のフィールドプレート構造を採用した。

## 結 果

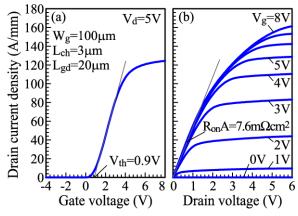

図 2(a), (b)に作製した EID-HEMT の  $I_d$ - $V_g$ 特性 と  $I_d$ - $V_d$  特性をそれぞれ示す。しきい値電圧が 0.9V のノーマリオフ動作と  $7.6m\Omega cm^2$  のオン抵抗が得られた。また、ゲート電圧 0V にて測定したオフ耐圧は 1kV を超える値が得られており、提案した EID AlGaN/GaN MOS-HEMT にて低オン抵抗/高耐圧のノーマリオフ動作が実証された。

[1] T. Nanjo et al., Electron. Lett 57, 670 (2021)

Figure 2. DC characteristics of EID-HEMT