# Si パターン基板上への Ge エピタキシャル層の CVD 成長

CVD growth of Ge epitaxial layer on patterned Si substrate 豊橋技科大<sup>1</sup>, SUMCO<sup>2</sup> °(M1)Mohd Faiz Bin Amin<sup>1</sup>, Jose A. Piedra-Lorenzana<sup>1</sup>, 飛沢 健<sup>1</sup>, 中井 哲弥<sup>2</sup>, 石川 靖彦<sup>1</sup> Toyohashi Univ. Tech.<sup>1</sup>, SUMCO<sup>2</sup>, °Mohd Faiz Bin Amin<sup>1</sup>, Jose A. Piedra-Lorenzana<sup>1</sup>,

Takeshi Hizawa<sup>1</sup>, Tetsuya Nakai<sup>2</sup>, Yasuhiko Ishikawa<sup>1</sup> E-mail: mohd.faiz.bin.amin.mr@tut.jp, ishikawa@ee.tut.ac.jp

### 1. Introduction

Epitaxial growth of Ge layer on Si has been used in the fabrication of near-infrared photodetectors in Si photonics. A high-quality Ge layer is required for the high-performance devices despite a large lattice mismatch of 4% between Ge and Si. Recently, we reported that the threading dislocation density (TDD) is significantly reduced in a coalesced layer of Ge selectively grown on an array of Si strip structures on Si-on-insulator (SOI) substrate [1]. The TDD reduction is derived from a downward bending of the dislocations, which are penetrated to the sidewall surface of SOI strips as well as to the surface of void overlying the bared SiO<sub>2</sub> surface between the SOI strips. In this work, a coalesced layer of Ge is studied, which is grown on an array of strip structures on bulk Si substrate.

#### 2. Experimental procedure

Using a photolithography and a dry etching, a bulk Si (001) surface was patterned into a periodic strips running in the [110] direction. The strip width was changed as a parameter ( $0.3 \mu m$ ,  $0.5 \mu m$ , and  $1.5 \mu m$ ), while the height (220nm) and spacing (0.5  $\mu m$ ) were fixed. Then, a 1- $\mu$ m-thick Ge layer was epitaxially grown by ultrahigh vacuum chemical vapor deposition at 700°C using a source gas of GeH4. The structures were evaluated by cross-sectional transmission electron microscopy (TEM).

## 3. Results and discussion

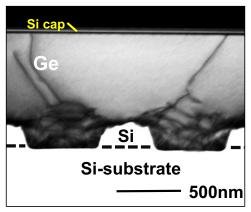

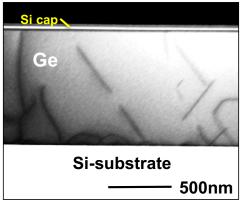

Fig. 1(a) shows a typical cross-sectional TEM image of a Ge layer grown on an array of 0.5-µm-wide array of strip structures on Si. A continuous layer of Ge with a flat surface was realized. Dislocations were observed in the coalesced Ge layer. which were mostly accumulated between the Si strips. The dislocations in the Ge layer were probably terminated at the strip surfaces and sidewalls, suggesting that the dislocations tend to be terminated by the misfit dislocations at the Ge/Si interface, instead of the penetration to the top surface. This dislocation behavior is considerably different from the blanket Ge layer on an unpatterned Si substrate. As in Fig. 1(b), the

dislocations were mostly directed to the top surface. A possible reduction in the threading dislocation density is anticipated, although a etch-pit density measurement is in progress to quantitatively evaluate the TDD in the coalesced Ge layer.

(a) Ge on strip-patterned Si

(b) Ge on unpatterned Si Fig. 1. Typical cross-sectional TEM images.

#### 4. Summary

A Ge epitaxial layer was grown on an array of strip structures on bulk Si. A continuous layer of Ge with a flat surface was formed. The dislocations showed an accumulation between the Si strips, suggesting a possible reduction in the threading dislocation density.

[1] Mohd Faiz Bin Amin et al., 2021 JSAP Fall Meeting, 10p-N202-2.