## SiC プラットフォームを用いた THz 波検出器の提案

**THz-Wave Detector on SiC Platform**

北里大<sup>1</sup>, 阪大基礎工<sup>2</sup>, NEL テクノ<sup>3</sup> <sup>○</sup>伊藤 弘<sup>1</sup>, 柴田紀彦<sup>2</sup>, 永妻忠夫<sup>2</sup>, 石橋忠夫<sup>3</sup>

Kitasato Univ. 1, Osaka Univ. 2, NEL Techno3

°Hiroshi Ito<sup>1</sup>, Norihiko Shibata<sup>2</sup>, Tadao Nagatsuma<sup>2</sup>, Tadao Ishibashi<sup>3</sup>

E-mail: h.ito@kitasato-u.ac.jp

導波管入力型の THz 波検出器では、導波管と検出器の接続に導波管カップラーや平面型回路が用いられるが、素子との接続部における信号の反射や損失を防ぐにはモノリシック化が望ましい。その手法として、検出器に用いる半導体基板自体を薄層化する構成、石英基板上に検出器を貼付ける構成、Si 基板上に検出器を貼付ける構成などが用いられている。しかしこれらの構成では、基板の脆弱性や、薄層化・小型化への限界などが課題であった。本報告では、これらを解決する手法として「SiC プラットフォーム」の適用を提案する。SiC 基板貼付けは、高出力素子の放熱に有効[1]なだけでなく、機械的強度が高く薄層化も容易であり、高周波損失が低く微細化や VIA 加工も可能なことから、THz デバイスにも適している。我々は、SiC プラットフォーム上に「フェルミレベル制御バリア (FMB) ダイオード」[2]を作製し、ヘテロダイン検波特性を検討した。

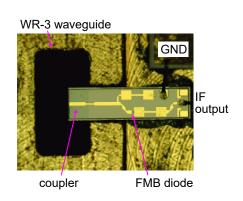

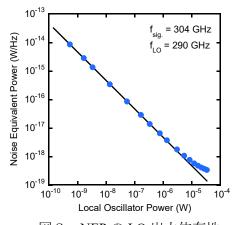

図1に、WR-3 導波管入力型筐体に実装した FMB ダイオードチップを示す。素子作製では、まず InP 基板上に成長した FMB ダイオード用のエピ層を SiC 基板上に転写し、次に作製したダイオード部だけを残してエピ層を除去した後、SiC 基板上に導波管カップラー及びフィルター回路を集積した。図2に、基本波ミキシング時(@300GHz 帯)の雑音等価電力(NEP)の局部発振器(LO)出力依存性を示す。NEP は LO 出力に反比例して低下し、やがて飽和傾向を示した。得られた NEP の最小値( $3\times10^{-19}$  W/Hz)は、これまで FMB ダイオードで得られた NEP として最も低い値である。またこのとき必要な LO 出力は僅か  $30\mu$ W であった。これらの結果は、SiC プラットフォームが THz 波検出器への適用に有効なことを良く示している。SiC プラットフォームは、発振器や逓倍器などの他の THz デバイスへの適用にも効果的な手法と考えられる。

[1] T. Sanjoh et al., JJAP **58**, SBBE06-1 (2019). [2] H. Ito and T. Ishibashi, JJAP **56**, 014101-1 (2017).

図1:導波管筐体に実装した FMB ダイオード

図2:NEPのLO出力依存性