## SiC 相補型 JFET 論理ゲートの 350℃動作

SiC complementary JFET logic gate operation at 350 °C

## 京大院工 ○金子 光顕、中島 誠志、金 祺民、木本 恒暢

°Mitsuaki Kaneko, Masashi Nakajima, Qimin Jin, Tsunenobu Kimoto (Kyoto Univ.) E-mail: kaneko@semicon.kuee.kyoto-u.ac.jp

SiC JFET は酸化膜をデバイス構造に使用しておらず、高温環境で動作可能な論理回路形成用の素子 として有望視されている。著者らは、n チャネル JFET (nJFET) と pJFET を組み合わせた相補型 JFET (CJFET) による集積回路の作製を提案しており、イオン注入による nJFET および pJFET の同一基板 上への作製とその 400℃動作を報告した[1]。本研究では提案した構造の nJFET および pJFET を用いて 相補型論理ゲートを実際に作製し、その高温動作が確認できたので報告する。

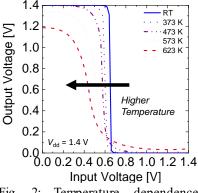

4H-SiC 高純度半絶縁性基板を使用した。作製した CJFET インバータの構造模式図および回路図を図 1に示す。p型およびn型領域は全てイオン注入で作製している。ゲートおよびチャネルのドーピング 密度は 5×10<sup>19</sup>および 5×10<sup>16</sup> cm³とした。イオン注入を行った後、1650℃、10 分の活性化アニールを 行った。CJFET インバータを構成する pJFET および nJFET の閾値電圧は-0.63 および 0.61 V である。 電源電圧は1.4Vとした。

室温~350℃における CJFET インバータの伝達 特性を図 2 に示す。いずれの温度でも良好なイ ンバータ特性が得られている。室温~350℃にお ける論理閾値電圧シフトは約0.2Vと非常に小さ く抑えられている。作製した JFET の構造パラメ ータを用いて解析式[2]から導出した室温~350℃ における論理閾値電圧シフト量は約 0.17 V とな

り、実験値と良い一致を示した。このことは、室温から高温域 にわたって CJFET 論理ゲートの特性予測が容易であることを 示している。一方、室温~200℃では rail-to-rail 出力が得られて いるものの、300℃以上では 0V入力時の出力電圧がわずかに 減少している。これは、300℃以上の高温域でpJFETのソース (電源) から nJFET のソース (接地) へ流れるリーク電流が 増大することが原因であり、このリーク電流の抑制がさらな る高温動作実現に向けた課題となる。

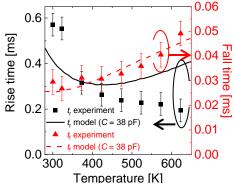

CJFET インバータの動特性における立ち上がり時間と立 下り時間の温度依存性を図3にシンボルで示す。 温度上昇と 共に立ち上がり時間は短くなるのに対し、立下り時間は長くな ることがわかる。立ち上がり時間は主に pJFET の特性を反映 し、温度上昇と共にドーパントのイオン化率が上昇することで ドレイン電流が増大するため、立ち上がり時間は短くなる。一 方、立ち下がり時間は主に nJFET の特性を反映し、温度上昇 と共に移動度の低下が生じるため、立下り時間は長くなる。伝 達特性の計算に用いた解析式により導出した立ち上がり時間 および立下り時間の温度依存性の計算結果を図 3 に実線、点 線で示す。立ち上がり時間に若干の乖離が見られるものの、 実験値と良い一致を示しており、動特性においてもCJFET論

理ゲートの特性予測が可能であることが示唆された。

p-JFET

Fig. 1: A schematic diagram of the fabricated SiC CJFET and an inverter circuit diagram.

Fig. 2: Temperature dependence of voltage transfer characteristics.

Fig. 3: Temperature dependence of rise and fall time of the SiC CJFET inverter.

[1] M. Nakajima et al., IEEE EDL 40, 866 (2019). [2] S. M. Sze, Semiconductor Devices Physics and Technology (Wiley, 2007).