## ミニマルファブ SOI CMOS におけるオーバーラップ長縮小の検討

Investigation of Shrinkage of Overlap Length of SOI CMOS of Minimal Fab

$^{\circ}$ 浜本 毅司  $^{1}$ , 北山 侑司  $^{3}$ , 丸山 智史  $^{3}$ , クンプアン ソマワン  $^{1,2}$ , 柴 育成  $^{3}$ , 原 史朗  $^{1,2,4}$   $^{1}$  ミニマルファブ推進機構、 $^{2}$ 産総研、 $^{3}$  横河ソリューションサービス、 $^{4}$ (株)Hundred Semiconductors

MINIMAL <sup>1</sup>, AIST <sup>2</sup>, Yokogawa Solution Service Corp.<sup>3</sup>, and Hundred<sup>4</sup>

°Takeshi Hamamoto<sup>1</sup>, Yuji Kitayama<sup>3</sup>, Satoshi Maruyama<sup>3</sup>, Sommawan Khumpuang<sup>1, 2</sup>, Yasunari Shiba<sup>3</sup>, and Shiro Hara<sup>1, 2, 4</sup> E-mail: takeshi.hamamoto@minimalfab.com

【背景】ミニマルファブは多品種少量生産をターゲットとした生産システムである[1]。このミニマルファブでのデバイス適応実績としては、カンチレバーに代表される MEMS デバイス、CMOS およびそれを用いた Ring Oscillator とオペアンプなどが試作されてきた。1,000Gate レベルの集積回路の動作検証は既に終了し、試作ファブとして実用化されている。今後は、PDK(Process Design Kit)を作成し、広範なユーザー設計に基づいた回路動作に対応すべく、MOSFET の動作精度向上、プロセスロバスト性確保に注力する段階となっている。今回、MOSFET のサイズ縮小の一環として、オーバーラップ長(以下、Lowと記す)縮小の検討を行った結果を報告する。

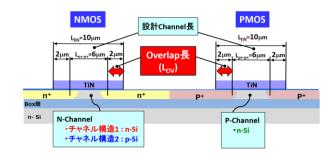

【MOSFET 構造】図1にミニマルファブ SOI CMOS の断面構造を示す。ゲート後作り構造を採用しており、TiN から成るゲートとソース/ドレインは非セルフアラインとなっている。そのため、ゲートとソース/ドレインのオーバーラップ長 Low として、リソグラフィー工程での合わせずれに対する余裕を持たせ 2μm に設定している。設計チャネル長は 6μm である。

## 【MOSFET 特性の Lov 依存性】

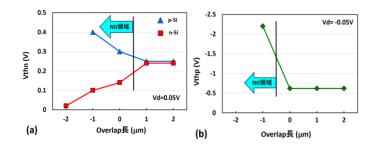

図 2 に閾値の  $L_{ov}$  依存性を示す。 (a) NMOS に於いては、p-Si と n-Si で逆の依存性を示している。p-Si チャネル構造では  $L_{ov}$  を縮小するにつれて、n+型拡散層とゲート電極間に閾値の高いオフセット領域が形成され、MOSFET全体の閾値も上昇すると考えられる。一方、<math>n-Si チャネル構造は、ゲート材料である TiN の仕事関数を制御することにより、デプレッション型 MOS の閾値をプラス側にシフトさせたデバイスである。そのため、 $L_{ov}$  を縮小するとゲート支配力が弱まり、閾値が低下するものと思われる。両チャネル構造とも、 $L_{ov}$  は現状の  $2\mu m$  に対して  $1\mu m$  までは同等であるが、それ以下に縮小すると閾値変動が発生する。一方、(b) PMOS に於いては、 $L_{ov}$  ( $0\mu m$  の領域ではオフセットが生じ、閾値が上昇する。

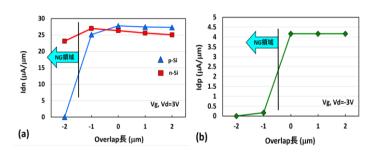

図 3 に電流駆動能力の  $L_{ov}$  依存性を示す。(a) NMOS は  $L_{ov}$ < $(-1\mu m)$ 、(b) PMOS は  $L_{ov}$ < $(0\mu m)$ 、の領域ならば電流駆動力の減少は見られない。

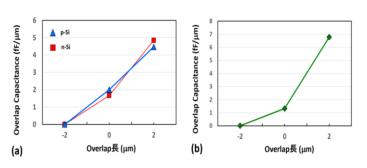

図 4 にゲート-ソース間、またはゲート-ドレイン間のオーバーラップ容量と  $L_{OV}$  の関係を示す。(a) NMOS、(b) PMOS とも  $L_{OV}$  を縮小すると容量が減少する。 $L_{OV}$  を縮小すると、高周波特性の改善が期待出来る。

図1 ミニマルファブ SOI CMOS 断面構造

図2 VthのOverlap長依存性

図3 IdのOverlap長依存性

図4 Overlap容量のOverlap長依存性

【参考文献】[1]原史朗、クンプアン ソマワン:「ミニマルファブの開発とそのデバイスプロセス」, 応用物理学会誌 83(5), p.380(2014).

この成果は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の助成事業(JPNP12004)の結果得られたものです。