## シリコンビアホールエッチングにおけるテーパー角制御の研究

## Study on taper angle control in Silicon via hole etching

○田中 宏幸<sup>1</sup>, 徳永 博司<sup>2</sup>, 野沢 善幸<sup>3</sup>, 速水 利泰<sup>3</sup>, クンプアン ソマワン<sup>1,4</sup>, 原 史朗<sup>1,4,5</sup> (<sup>1</sup>産総研, <sup>2</sup>MTC, <sup>3</sup>SPP テクノロジーズ, <sup>4</sup>ミニマルファブ推進機構, <sup>5</sup>Hundred Semiconductors)

°H. Tanaka<sup>1</sup>, H. Tokunaga<sup>2</sup>, Y. Nozawa<sup>3</sup>, T. Hayami<sup>3</sup>, S. Khumpuang<sup>1, 4</sup>, and S. Hara<sup>1, 4</sup> (<sup>1</sup> AIST, <sup>2</sup> MTC, <sup>3</sup> SPPT, <sup>4</sup> MINIMAL, <sup>5</sup> Hundred) E-mail: tanaka.hiroyuki@aist.go.jp

## 【 背景・目的 】

半導体の製造は、一般にシリコンウェハに回路を作り込む前工程とウェハからチップを切り出してパッケージング(実装)する後工程に大別される。この前工程においては、これまでICチップの性能向上を実現してきた微細加工が物理的限界に近づいている。そのため、高機能化や多機能化を実現するために後工程プロセスが重要視されるようになった。具体的には、ロジックチップやメモリー、アナログデバイス、センサーなどを一つのパッケージに統合して3次元実装することにある。これらの目標を達成する究極のパッケージング技術として期待されてきたのが、シリコン貫通ビア(TSV: Through Silicon Via)技術である。TSV技術による3D ICは、シリコン貫通ビアを電極として上下のシリコン積層ダイをマイクロバンプによって電気的かつ機械的に接続することが可能となる。ただし、その製造は、それほど容易でなく、何より製造コストが掛かることから、TSV技術による3D ICへの移行は、当初の期待どおりに普及していないのが現状である。

ミニマルファブ<sup>1</sup>では、TSV を実装の中核構造として位置づけ、TSV の中核技術である深掘り Bosch Process<sup>2</sup>をミニマルファブでのプロセス開発の最重要課題の一つとしている。我々は、この Bosch Process を用いて 250µm 厚のハーフインチウェハに TSV 深掘りエッチング技術の開発を行ってきた<sup>3</sup>。Bosch Processで TSV 深掘りエッチングを行うには、Si 基板を所望の深さのエッチングまで次工程以降の絶縁層形成やシードスパッタ形成の妨げとならないよう、僅かに順テーパー形状となることが望ましい。

ところが、パッシベーションとエッチングのガス分子置換に不利な、穴が狭の場に不利な、穴形状の場に不利な、アーパー形状作りは容易でないチール形状作りは容易でないチールでなる。 進行方向に位置する Si 表面に CF エス系・プラールで表面に位置する Si 表面に CF エス系・プラールである。 進行しなくなるか、逆に完全除となるが全く進行しなくなるか、が全く進行しなくなるか、があった。 が全く進行しなくなるが、のテールを場合、 あいたのデーを作り出すには、このプロセスを関する。 のテールを作り出すには、このプロセスを関する。 のデーを作り出する。 のデーを作り出する。 のデーを作り出する。 のデーを作り出する。 のデーを作り出する。 のデーを作り出する。 のデーを作り出する。 のデーを作り出する。 のデーを作りまる。 のデーをであるが、 のデーをである。 のデーをできる。 のできる。 ので

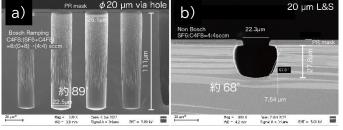

Fig.1 a) Bosch Ramping Etching Process, Press. 10Pa, ICP 40W,  $C_4F_8$ :  $(SF_6 / C_4F_8) = 8$ :  $(8 / 0 \rightarrow 4 / 4)$  sccm, Time = 81 min. b) Non-Bosch Isotropic Etching Process, Press. 10Pa, ICP 40W, SF<sub>6</sub>:  $C_4F_8 = 4$ : 4 sccm, Time = 20 min.

さ、研究レベルではあまり求められないが、実用上は極めて重要)を得ることができなかった。一方、Non-Bosch プロセスの場合は、マスク裏面のサイドエッチと対マスク選択比が十分に得られないことによる深掘りの困難さそのものが課題であった。

そこで、この問題に対して、Bosch Process 方式でありながらエッチングステップの  $SF_6$ に  $C_4F_8$  ガスを微量添加させることで、微少なテーパーを維持したシリコンビアホールを形成することができた。本稿では、これらのエッチングメカニズムの手法と解析結果を報告する。

## 【 実験結果と考察 】

我々が開発した Bosch Process 装置は、エッチング異方性を高めるためプラズマシース (sheath) を発生させてウェハ基板側からバイアス (2MHz, Vpp 300V) を印加させる  $SF_6$  等方性エッチングプロセスと、パッシベーション膜を生成する  $C_4F_8$  プロセスが交互に実施される様に構成されている。通常、それぞれのプロセスは、数秒間ずつガスが混じり合わない様に供給され、これを繰り返し行うことで深掘りエッチングを実現している。これに対して、 $SF_6$  を用いるエッチングプロセス中に意図的にパッシベーションの  $C_4F_8$  ガスを添加させると、Bosch Process でありながら、僅かながらテーパー角(垂直 90° に対して、約 89°) がついたビアホールを容易に形成できた(図 1 a)。Non Bosch Process(図 1 b)や、メタルマスクを用いたマスク裏面サイドエッチを行う Bosch Process<sup>4,5</sup> は、間口を広げてテーパー形状を作り出す方法である。これに対し、 $C_4F_8$  ガス添加 Bosch 方式では、マスクを十分に保護しながらサイドエッチを極力抑えられる点で有利である。また、通常の深掘り方式よりテーパーを形成するプロセスマージンが大きい。

<謝辞>この成果の一部は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の助成事業(JPNP12004)の結果で得られたものである。

- [1] 原 史朗, クンプアン ソマワン, 「ミニマルファブの開発とそのデバイスプロセス」, 応用物理, 83(5), 380 (2014).

- [2] F. Laermer, A. Schilp, K. Funk, M. Offenberg: "Bosch deep silicon etching: Improving uniformity and etch rate for advanced MEMS applications", Proc. 12th International Conf. on Micro Electro Mechanical Systems (MEMS'99), pp. 211-216 (1999).

- [3] H. Tanaka, S. Khumpuang, S. Hara: "Small Plasma Space with a Small Plasma Source and Its Advantage in Minimal Fab", J. Photopolym. Sci. Technol., 32(5), pp.747-752 (2019).

- [4] Zhong Ren, Mark E. McNie: "Inductively coupled plasma etching of tapered via in silicon for MEMS integration" Microelectronic Engineering Vol. 141, 15 June 2015, pp 261-266

- [5] Niclas Roxhed, Patrick Griss, Goran Stemme: "Tapered Deep Reactive Ion Etching: Method and Characterization" The 14th International Conference on Solid-State Sensors, Actuators and Microsystems Conference, Lyon, France 10-14 June 2007