## ミニマルファブを用いた3軸ピエゾ抵抗型加速度センサの性能改善と MEMS デバイス歩留確認手法の検討

Process Improvement of three-axes Piezo-resistive Accelerometer and Development of MEMS

Device Yield Check Method in Full Minimal-Fab Process

ミニマルファブ推進機構  $^1$ , 産業技術総合研究所  $^2$ , (株)Hundred Semiconductors  $^3$   $^{\circ}$ 小粥 敬成  $^1$ , 田中 宏幸  $^2$ , 居村 史人  $^{2,3}$ , クンプアン ソマワン  $^{1,2}$ , 原 史朗  $^{1,2,3}$

MINIMAL<sup>1</sup>, AIST<sup>2</sup>, and Hundred<sup>3</sup>

Hiroshige Kogayu<sup>1</sup>, Hiroyuki Tanaka<sup>2</sup>, Fumito Imura<sup>2, 3</sup> Sommawan Khumpuang<sup>1, 2</sup>, and Shiro Hara<sup>1, 2, 3</sup> E-mail: hiroshige-kogayu@minimalfab.com

[背景・目的] MEMS デバイスの多品種少量性は、我々が実用化したミニマルファブに適していることから、当初から装置の開発と共に MEMS デバイスの開発も進めてきた[1]。これまで、様々な MEMS デバイスの試作を行ってきたが[2][3][4]、ボッシュプロセスによる高精度の深掘りエッチング技術を用いて MEMS デバイスの構造を制御し[5]、ピエゾ抵抗型1軸、2軸及び3軸加速度センサを試作して、その基本特性および加速度特性を得ることができた[6][7][8]。そこで我々は3軸加速度センサの性能向上を図るとともに、ハイブリッドデバイス作製を目指した PMOS トランジスタの同時形成、さらに今後の生産フェーズを睨んでフルミニマルプロセスを用いた MEMS 歩留の確認手法を検討した。本稿では、そのプロセス改良と歩留確認手法について、実験を行った結果を報告する。

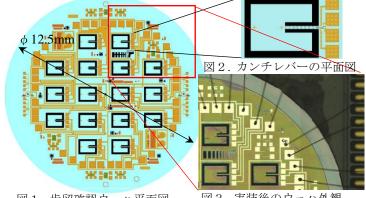

[作製、評価方法] 前回報告[8]した3軸加速度センサでは加速度特性を得ることができたが、ウェハ表と裏のパターンズレにより x 軸/y 軸方向で同等の感度が得られなかった。そこで今回は以下の項目に着目してプロセスの改良を行なった。①合わせズレの原因究明とプロセス改善;露光機をプロセス途中で変更することによるレンズ収差の機差による寸法ズレが主な原因とわかった。露光装置の変更、エッチング装置の条件出し等を行ない対応した。②PMOS トランジスタの同時形成;ピエゾ抵抗の拡散層保護酸化膜を熱酸化膜10nm+TEOS 膜300nmの構成からPMOSのゲート酸化膜として熱酸化膜60nmにプロセス変更した。また、ピエゾ抵抗のコンタクト抵抗改善としてH2シンタリングを行なっていたが、そのままゲート酸化膜のダメージ回復としてもH2シンタリングを活用した。以上のプロセス変更によりMEMSプロセスフローの中でPMOSトランジスタを作製した。次にMEMS 歩留の確認手法として簡便な方法で多数を確認できるよう、図1、2に示すよ

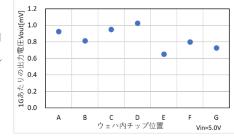

うカンチレバー(1軸加速度センサ)を16個配置して各端子をウェハ周辺に引出し、各チップを個別にパッケージせずにウェハをダイレクトに基板に実装し、ワイヤボンディングを行なった。図3に実装したウェハ外観を示す。MEMS特性はおもりに働く重力による梁の変形について、ウェハを表にした時の出力電圧を測定し、裏にして再度測定して、その出力電圧の差分から感度を算出した。

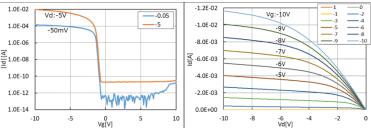

良によりズレは規格内に収束できることが確認できた。3 軸加速度センサの各軸感度は確認中である。(2)同時に形成したPMOSトランジスタ(L=6μm、W=100μm、tox=60nm)の特性を図4に示す。正常なトランジスタ特性が得られた。(3)図 5 にカ

[結果と考察] (1)合わせズレのプロセス改

ンチレバーの出力電圧特性を示す。7個の平均で0.84mV/G(@Vin=5V)であり、ウェハ実装で特性が得られ、歩留確認でき

ることが分かった。n 増しを実施中であり、詳細は当日の報告で述べる。

図1. 歩留確認ウェハ平面図

図3. 実装後のウェハ外観

図4.PMOS トランジスタの Id-Vg、Id-Vd 特性

## <参考文献>

- (少与文献/)

[1] 原史朗, クンプアンソマワン, 「ミニマルファブの開発とそのデバイスプロセス」, 応用物理, 83(5), 380 (2014).

- [2] クンプアンソマワン、「ミニマルファブにおけるデバイスプロセス開発事例」, クリーンテクノロジー, Vol.23. No.12 (2014).

- [3] Y. X. Liu et al., Jpn. J. Appl. Phys. 57, 06HD03-1-6, 2018.

- [4] Tuan Anh Phan,他,第 78 回応用物理学会秋季学術講演会 6p-C21-13(2017).

- [5] 田中宏幸,他,第 79 回応用物理学会秋季学術講演会 21p-233-7(2018).

- [6] 小粥敬成, 他, 第 68 回応用物理学会春季学術講演会 19p-Z24-5(2021).

- [7] 小粥敬成, 他, 第 69 回応用物理学会春季学術講演会 24a-E102-6(2022).

- [8] 小粥敬成, 他, 第 83 回応用物理学会秋季学術講演会 20p-A406-13(2022).

図 5 .加速度に対する出力電圧

謝辞:この成果は、国立研究開発法人新エネルギー・産業技術総合開発機構(NEDO)の助成事業(JPNP12004)の結果得られたものです。