## 強誘電体トンネル接合の電荷トラップ影響シミュレーション

Simulation Study on the Effects of Charge Traps in a Ferroelectric Tunnel Junction

東大生研 <sup>1</sup>, 東大 d.lab<sup>2</sup> <sup>O</sup>(M2)金 在顕 <sup>1</sup>, 更屋 拓哉 <sup>1</sup>, 平本 俊郎 <sup>1</sup>, 小林 正治 <sup>1,2</sup>

<sup>1</sup>HS, Univ. of Tokyo, <sup>2</sup>d.lab, Univ. of Tokyo <sup>O</sup>Jaehyun Kim <sup>1</sup>, Takuya Saraya <sup>1</sup>, Toshiro Hiramoto <sup>1</sup>

and Masaharu Kobayashi <sup>1,3</sup>

E-mail: jh-kim@nano.iis.u-tokyo.ac.jp

【背景・目的】 $HfO_2$  系強誘電体による強誘電体トンネル接合(FTJ) は、高密度データ保存、非破壊読み出し、高速書き込み/読み出し動作および CMOS プロセスとの整合性など、多様な利点により次世代不揮発性メモリとして注目されている[1-3]。FTJ の性能指標は、強誘電体の分極反転によるトンネル電気抵抗比 (TER) である。しかし、TER や信頼性に影響を与える、強誘電体層に生成される電荷トラップの影響に関する調査は少ない[4]。本研究では、TCAD を用いて  $Hf_{0.5}Zr_{0.5}O_2(HZO)$ をトンネル層とする FTJ モデルを構築し、強誘電体分極反転と HZO 内の電荷トラップが TER に与える影響をシミュレーションのよって調査した。

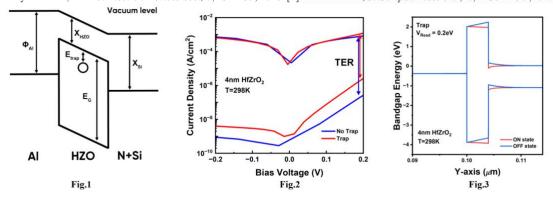

【シミュレーション方法】本研究では、金属-強誘電体-半導体(MFS)構造の FTJ を想定し、モデルを構築した。このデバイスのバンドダイアグラムの模式図を Fig. 1 に示す。パラメータは以下の通りである。Si 基板の N<sup>+</sup>ドーピング濃度  $10^{19}\,\mathrm{cm}^3$ 、電子親和力 $X_{Si}=4.05\,\mathrm{eV}$ 、HZO の膜厚  $4\mathrm{nm}$ 、HZO の Bandgap  $E_G=4.05\,\mathrm{eV}$ 、電子親和力 $X_{HZO}=2.0\,\mathrm{eV}$ 、トラップレベル $E_{trap}=4.05\,\mathrm{eV}$ 、トラップ濃度  $10^{19}\,\mathrm{cm}^3$ 、飽和分極 $P_r=5\mu C/\mathrm{cm}^2$ 、Al の仕事関数 $\Phi_{Al}=4.05\,\mathrm{eV}$ 。電荷トラップのパラメータは HfO2 系強誘電体の先行研究の値を参考にしている。電流成分には Nonlocal tunnel モデルを使用し、直接トンネル・Fowler-Nordheim トンネルに加えて、Trap-assisted トンネル成分を導入した。

【実験結果】 本 MFS 構造 FTJ に対して+2.0V/-2.5V の範囲で電圧を掃引したときの電流-電圧の読出し特性を Fig.2 に示す。今回は分極反転に関しては静特性のみ考慮している。まず電荷トラップが無い場合、分極反転に伴い実効的なトンネル障壁高さが変調されることにより TER が現れることを確認した。一方、電荷トラップが有る場合、オン電流の電流値は電荷トラップ無しの場合に比べて変化が小さいが、オフ電流の電流値が一桁以上増大していることがわかる。これにより TER が減少し、センシングマージンが低下することが示唆される。書き換え回数が増加するにつれて電荷トラップ密度は増加することが予想され、それによってセンシングマージンが書き換えと共に劣化することが懸念される。講演ではトラップの位置やトラップ密度に対する依存性や、金属電極や絶縁膜を導入したモデル等についても報告する予定である。今後は実験によるキャリブレーションによりモデルの精度を高め、HfO2系 FTJ のメモリとしての実用可能性を明らかにしていく。

【まとめ】TCADを用いてMFS構造の強誘電体トンネル接合モデルを構築し、強誘電体の分極反転と 電荷トラップによる電流一電圧特性をシミュレーションで調査した。その結果、オフ電流の増加によ り TER が減少し、センシングマージンが劣化することを確認した。

【文献】[1] V. Garcia et al., *Nat Comm.*, **5**, 4289, 2014. [2] F. Ambriz-Vargas et al., *ACS Appl. Mater. Interfaces*, **9**, 15, 13262–13268, 2017. [3] M. Kobayashi et al., *IEEE J. Electron Devices Soc.*, **7**, 134–139, 2018. [4] M. Pešić et al., *J. Comput. Electron.*, **16**, 1236–1256, 2017.

Fig.1 Band diagram of TCAD model of FTJ Fig.2 Simulated I-V curves Fig.3 Bandgap plots at the read voltage