## 半導体スピン素子のための高濃度 p型 Si 層の作製

Fabrication of heavily-doped *p*-type Si layer for semiconductor based spin devices

日大工¹ ○石川 瑞恵¹

Nihon Univ. College of Engineering <sup>1</sup>, <sup>o</sup>Mizue Ishikawa<sup>1</sup> E-mail: ishikawa.mizue@nihon-u.ac.jp

## 1. はじめに

半導体スピン素子は半導体エレクトロニクスの更なる小型化・高速化・低消費電力化への貢献が期待できる,極めて重要な電子デバイスとして注目されている。我々はこれまで強磁性体/MgO/ $n^+$ Siからなる半導体スピン素子を作製し, $n^+$ -Si中でのスピン伝導の室温観測に成功している[1]. 半導体スピン素子の実用化には $n^+$ -Si中でのスピン伝導のみならず, $p^+$ -Si中でのスピン伝導を実証していく必要がある。前回,半導体スピン素子のための高濃度 $p^+$ -Si層を作製した結果,拡散アニール温度に依存した層表面の形状変化や表面粗さの増大を確認した。これまでの研究より,表面粗さが大きいとスピン信号強度が低下することを明らかにしている[2]. そこで本研究では,高濃度 $p^+$ -Si層の作製条件の見直しを行い,作製条件と表面形状の関係について評価した。

## 2. 実験結果

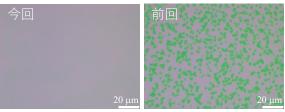

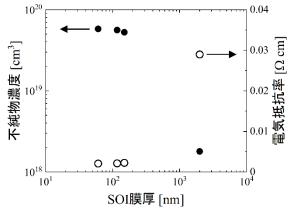

基板洗浄した SOI(001)基板(117 nm)上に, ボロ ン(B)がドープされた PBF 液を塗布し, 600°C の 酸素雰囲気中でのプリベーク後,850℃の窒素雰 囲気中での拡散アニールを行った. 次に酸化膜を 剥離後, ケミカル酸化膜を形成し SOI 層にドープ された B を拡散・活性化させるため 980°C で窒 素雰囲気中でのアニールを行った. 作製した高濃 度  $p^+$ -Si 層において、四探針法によりシート抵抗 を測定し不純物濃度(p)を算出した結果,  $p \sim 5.61$  $\times 10^{19}$  /cm<sup>3</sup> となった. この  $p^+$ -Si 層表面の光学顕 微鏡写像を Fig. 1 に示す.比較のため,前回作製 した $p^+$ -Si層表面についても合わせて示す. 今回, 作製条件を見直すことにより、表面にあったボイ ド状の凹凸を抑制することに成功した. また不純 物濃度の SOI 膜厚依存性について評価した結果 を Fig. 2 に示す. Fig. 2 より, SOI 膜厚に依存し

**Fig. 1.** Optical microscope images for fabricated heavily-doped SOI substrates.

**Fig. 2.** Dependence of impurity concentration and resistivity on SOI thickness.

て不純物濃度が変調できていることがわかる. 当日は、作製条件の詳細や $p^+$ -Si層の表面粗さ評価についても報告する. 本研究の一部は、科学研究費補助金(21K14213)の支援を受けて行われた.

[1] M. Ishikawa et al., IEEE Trans. Magn. 54, 1400604 (2018). [2] M. Ishikawa et al., MMM2014 (2014).